����FPGA��ͨ�î����հl���OӋ

ժҪ������Verilog HDL�Z������Ӳ�����ܵ��������\��ģ�K���OӋ�����քe�OӋ��ͨ�î����հl��(UART)�İl��ģ�K������ģ�K�Ͳ����ʰl���������Y�ϬF���ɾ����T���(FPGA)�����c�����F��һ������ֲ��UARTģ�K��ԓ�OӋ���H���F�˴��Ю���ͨ�ŵ���Ҫ���ܣ������·���Σ������������ɿ������Ԍ����`���Ƕ�뵽����ͨ��ϵ�y�С�

�P�I�~��ͨ�î����հl�����F���ɾ����T��У�Verilog HDL������ͨ��

����ͨ��Ҫ��Ă�ݔ���٣��ɿ��Ըߣ���ݔ���x�h�����V��������Ӌ��C�����O�Ĕ������Q��ͨ������ͨ�î����հl��(UART)�팍�F����ͨ�ŵĹ��ܡ��ڌ��H�����У�����ֻ��ҪUART�Ďׂ���Ҫ���ܣ����õĽӿ�оƬ������YԴ���M�ͳɱ���ߡ��S��FPGA��CPLD���w�ٰlչ�c���ڬF������OӋ�еďV�����ã�FPGA��CPLD�������_�l�^��Ͷ�YС�����ڶ̡��ɷ��;��̡������Ժõ����cҲԽ��Խ���@����˿��Գ���������YԴ����оƬ�ϼ���UART����ģ�K���Ķ��������·���sС���w�e������˿ɿ��ԣ������OӋ�r���`���Ը������ڸ��̡��b�ڴ˱��������һ�N����FPGA���FUART���ܵķ�����������Ч�ؽ�Q�������}��

1 UART�Ĺ���ԭ��

UART(Universal Asynchronous Receiver Transmitter��ͨ�î����հl��)�ǏV��ʹ�õĮ������Д�����ݔ�f�h���ڴ���ͨ���У��������ֹ����λ���ֹ����M�Ђ��͡��l�Ͷ˺ͽ��ն˱�횰�����ͬ���ֹ�����ʽ�Ͳ������M��ͨ�š�UART����������ݔ��һ�����Д�������1λ��ʼλ(���ƽ)��5��8λ����λ��1λУ�λ(���x)��ֹͣλ(�ɞ�1��1��5��2λ)����ʼλ���ֹ������_ʼ��ʹ������̎��߉0��B����������ն˱����_ʼ�l�͔���������ʹ�l�ͺͽ����O�䌍�Fͬ���Ĺ��ܡ�ֹͣλ���ֹ����ĽKֹ��ʹ������̎��߉1��B����������ն˱����������l���ꮅ�������ʲ��ؘ�����9 600 b��s�������ڂ�ݔ�r����λ��ǰ����λ�ں��ն˙z�y���_�J��ʼλ���Ք���λ��ֹͣ

λ�����ꮅ����CPU�l���Д���̖��ͬ�r�������l�͵�Ӌ��C��8λ���������ϣ��l�͔����r������CPU�O�ò����ʣ�Ȼ��8λ���Д���������ʼλ��ֹͣλ�l�ͽo���O��ֹͣλ�l���ꮅ����CPU�l���Д���̖���ڔ����l�ͺͽ����^���У�CPU����ͨ�^������̖���xȡUART�Ĺ�����B���Ա��M�Ќ��r̎����

2 UART��ģ�K���OӋ

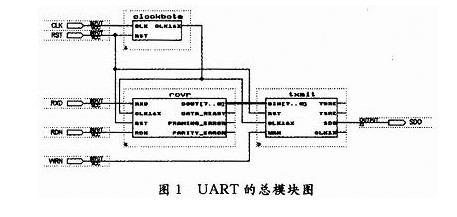

2��1 ϵ�y���w�Y��

�ڴ�Ҏģ�·���OӋ�У��V�����ÌӴλ����Y�������OӋ����������һ��������Ӳ���OӋ�΄Տ�ϵ�y���_ʼ�����֞����ɂ��ɲ�����ģ�K�����Ƴ�������ģ�Ͳ��M�з�����C���^����ϵ�y�����M�нM�ϡ��@��������OӋЧ�ʵ�ͬ�r��������OӋ�|������Ŀǰ���s����ϵ�y���F����Ҫ�ֶΣ�Ҳ�DZ����OӋ˼��Ļ��A������ϵ�y�����M�Є��֣�UART��Ҫ�ɲ����ʰl����������ģ�K�Ͱl��ģ�K���ֽM�ɡ���Maxp-lus�����h���£��ɸ�����ģ�K�M�оC�ϵ�ϵ�y��ģ�K��D1��ʾ������քeӑՓ�l��ģ�K������ģ�K�Ͳ����ʰl����ģ�K�ľ��w���F�^�̡�

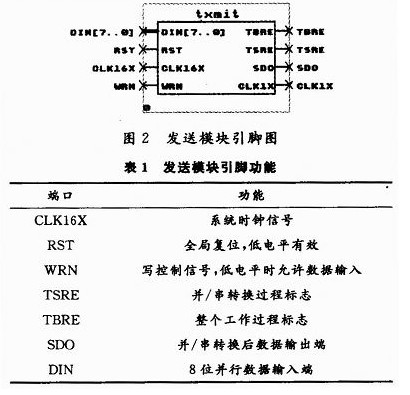

2��2 �l��ģ�K

2��2��1 �l��ģ�K���书��

�l��ģ�K��Ҫ���F�����Д����ľ��桢�����D�Q�����Ѵ��Д������ռȶ���������ʽ�M��ݔ�����l��ģ�K�����_��D2��ʾ�������_����Ҋ��1��

��CPU�́��Ĵ��l�͵IJ��Д��������Ȍ���l�;��_��TBR[7����0]���l�;��_�^���Д������l�͕r�������Ԅ��b����λ�Ĵ���TSR[7����0]���Ԅ���ɴ��Д����İl�͡����Ȃ���һλ��ʼλ0��Ȼ��������Y���ж��x�Ĕ����L�ȣ��քe�����Ƴ�TSR[7����0]�еĔ����������ĵ�λ��ǰ����λ�ں��]�Д����l�͵ĕr��SDO���_���ָ��ƽ��

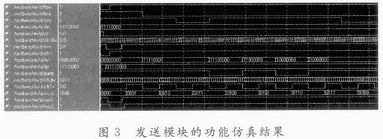

2��2��2 �l��ģ�K���ܷ���

�l�������ܷ���Y����D3��ʾ�����M�Ɣ�11110000�����_DIN[7����0]����ݔ�룬��WRN��0�r�����Ӱl�ͳ���Ӌ�����_ʼӋ����ʹ�l���������Д����i�浽�l�;��_��TBR[7����0]����ͨ�^�l����λ�Ĵ���TSR[7����0]��λ��λ�l�ʹ��Д��������Д���ݔ����SDO���ڔ����l���^������ݔ����̖TBRE��TSRE�����־��̖����һ�������ɰl�;��_��TBR[7����0]�͵��l����λ�Ĵ���TSR[7����0]�r��TBRE��̖��1���ɰl�͔������_�����o�l����λ�Ĵ�����Ҫ����̖TSRE���ơ���TSRE��1�r����ʾ�l����λ�Ĵ���TSR[7����0]���аl���ꮅ����0�r��ʾ߀�]

�аl����һ���������ɷ���Y����C�˰l��ģ�K�����_�ԡ�

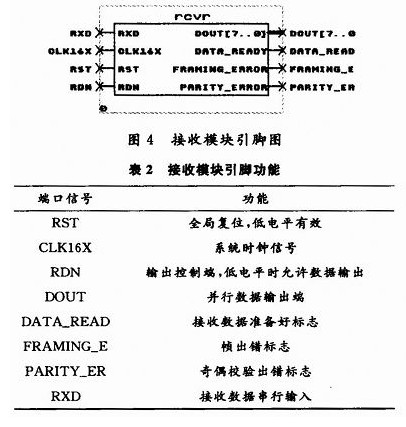

2��3 ����ģ�K

2��3��1 ����ģ�K���书��

����ģ�K�������ǰ��յ��Ĵ��Д����D�Q�ɲ��Д����M��ݔ�������Д��յ��Ĕ����Ƿ����e������ģ�K�����_��D4��ʾ�������_����Ҋ��2��

�������M��ʂ���Ք�����B������Oҕ����ݔ�뾀RXD�ˣ�������F���ƽ�����̆�����ʼλ�z�y�·�M�д_�J��һ���_�J����յ����_����ʼλ���t�Բ���������ɘӕr犣���ÿ������λ�����gλ�òɘ�һ�Σ����Ѳɘӵ�����Ϣ����λ��ʽ���˽�����λ�Ĵ���RSR�����յ�һ������λ�Ѵ��Д����D���ɲ��Д��������M����żУֹͣλ����ֹ�B�ęz�顣�����ꮅ��DAT_READ��1��

2��3��2 ����ģ�K���ܷ���

����ģ�K���ܷ���Y����D5��ʾ�����M�Ɣ�11101010�����_RXD����ݔ�룬��������Ҫ����ʼλ����RDN��̖��0�l���£����ӽ��ճ���Ӌ�����_ʼӋ����������RXD[7����0]����ݔ�룬�ɽ�����λ�Ĵ���RSR[7����0]��λ��λ���գ����ڽ�����ɕr���ͽo���վ��_�Ĵ���RBR[7����0]���^����վ��_�Ĵ���RBR[7����0]�����յĔ���������DOUT[7����0]����������ݔ����ͬ�rݔ��һ�����Ք����ʂ����̖DATA _RE��־���������ꮅ��

2��4 �����ʰl����ģ�K

2��4��1 �����ʰl����ģ�K���书��

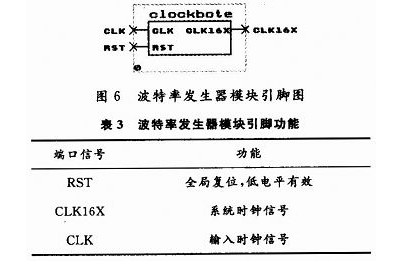

�����ʰl����ģ�K��Ҫ���ڮa������ģ�K�Ͱl��ģ�K�ĕr��l�ʣ��䌍�|����һ�����l�������Ը����o����ϵ�y�r��l�ʺ�Ҫ��IJ�������������ʷ��l���ӣ�������l���ķ��l���������ʰl�����a���ĕr��l��CLK16X���Dz����ʕr��l��CLK�����Dz����ʕr��l��CLK��16���������ʰl����ģ�K�����_��D6��ʾ���书�����3��ʾ��

2��4��2 �����ʰl�������ܷ���

UART�ڰl�ͻ���Ք����r��ʹ�õĕr���̖�l��f�Dz�����(b=9 600 b��s)��16�������ⲿϵ�y�r��M��16���l�õ���UARTÿ16�����ؕr犰l�ͻ����һ�����M��λ���OӋ�в��õľ����l��c=25 MHz����ô�����ʰl����ݔ���ĕr���̖���ڞ飺

![]()

�����ʰl�����Ĺ��ܷ�����D7��ʾ��

���OӋ�þ����25 MHz���ɹ�ʽ�ɵó�ݔ�����εİ낀���ڑ���k��2����81����ݔ��r����ڣ�����Y����C�˲����ʰl����ģ�K�����_�ԡ�

3 �Y�Z

UlART�ǏV��ʹ�õĴ��Д���ͨ���·������Ҫ��Ă�ݔ���٣��ɿ��Ըߣ���ݔ���x�h������ϵ�y�g�������î�������ͨ�Žӿڷ�ʽ��������Verilog HDL�Z�ԣ��Y�����ޠ�B�C���OӋ�������F��UART�Ĺ��ܣ�������Ĺ��ܼ��ɵ�FPGA�ϣ�ʹ���w�OӋ�o����С�ɣ����F��UART���ܷ������ɿ���ͬ�r���������ޠ�B�C�ķ������нY��ģʽֱ�^���Σ��OӋ���̶̣�����Ӵη������C�ϣ��ɿ��Ըߵȃ��c���،���EDA���g�аl�]��Ҫ���á�

���P��x:

- ...2012/03/31 10:53������FPGA�����l�x�����OӋ

- ...2011/12/02 16:57������FPGAֱ�����ДU�lϵ�y���OӋ

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��Ђ�ݔϵ�y���OӋ�c���F

- ...2011/11/07 15:10������FPGA���h���x�y��������ϵ�y�OӋ

- ...2011/10/31 16:02������FPGA�Ĕ����ɼ�ϵ�y�OӋ

- ...2011/10/31 16:02������FPGA�Ľ�ͨ��ϵ�y�����OӋ

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇