����FPGA�Ĕ�(sh��)��(j��)�ɼ�ϵ�y(t��ng)�O(sh��)Ӌ(j��)

ժҪ�����һ�N����FPGA���g(sh��)�Ķ�·ģ�M������(sh��)�����ɼ��c̎��ϵ�y(t��ng)���O(sh��)Ӌ(j��)��������������(g��)ϵ�y(t��ng)�ĽY(ji��)��(g��u)����ӑՓFPGA��(n��i)��Ӳ���YԴ�Ą��ֺ�ܛ�����O(sh��)Ӌ(j��)�����ȡ����O(sh��)Ӌ(j��)�����ⲿ�·�Y(ji��)��(g��u)���οɿ����e�m���ڶ�·�z�yϵ�y(t��ng)�У����ҿ��Ը���(j��)��Ҫ���،�ϵ�y(t��ng)�M(j��n)�ДU(ku��)չ�����ڙz�yϵ�y(t��ng)���v����һ����ͨ���ԡ�

�P(gu��n)�I�~��FPGA��A��D�ɼ�����(sh��)�����ɼ���Verilog HDL�Z���O(sh��)Ӌ(j��)

0 ����

��늚�y��ϵ�y(t��ng)�У�������Ҫ�ɼ����Nģ�M����̖����(sh��)������̖�����������M(j��n)������(y��ng)��̎����һ����r�£��y��ϵ�y(t��ng)������ͨMCU(��51��196�Ȇ�Ƭ�C(j��)�������DSP)�Ϳ������ϵ�y(t��ng)�΄�(w��)������(d��ng)ϵ�y(t��ng)��Ҫ�ɼ�����̖���e���r(sh��)(�e�Ǹ��N��̖������B(t��i)��)���H�H������ͨMCU���YԴ�������y������΄�(w��)�������������һ�N����FPGA���g(sh��)��ģ�M������(sh��)�����ɼ��c̎��ϵ�y(t��ng)������FPGA��I��O�˿ڶ࣬�ҿ������ɾ���֧�䡢���x�书�ܵ����c(di��n)���ܺܺõؽ�Q�ɼ�����̖·��(sh��)��Ć��}��

1 ϵ�y(t��ng)�M��

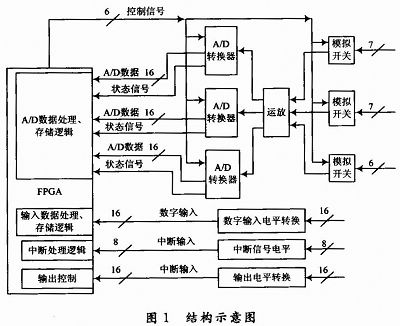

��ϵ�y(t��ng)�е�����·�O(sh��)Ӌ(j��)�������Ρ��ɿ������b��FPGA���������c(di��n)��ϵ�y(t��ng)�����^�õĔU(ku��)չ�ԣ��ڱO(ji��n)�y�Ϳ���ϵ�y(t��ng)��Ҳ����һ����ͨ���ԡ�ϵ�y(t��ng)��Ҫ������FPGAоƬ�^(q��)����·�x���cA��D�ɘ��·���r(sh��)��Դ�^(q��)��PROM���a���d�·�Ȏײ��֡��Y(ji��)��(g��u)ʾ����D1��ʾ��

2 FPGAоƬ���c(di��n)�������YԴ����

��ϵ�y(t��ng)�е�FPGA�Dz���Altera��˾��EP1C20F400��ԓϵ�еă�(n��i)�˲���1��5 V��늣�I��O�˿ڹ��늉���3��3V��

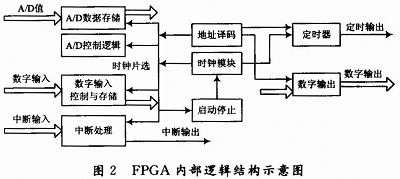

FPGA��(n��i)���YԴ���֞��Ĵ֣���D2��ʾ��

(1)FPGA߉�\(y��n)�����ġ��Á��������������ֵĔ�(sh��)��(j��)�������ճ������O(sh��)���ķ��������յ��Ĕ�(sh��)��(j��)�M(j��n)������(y��ng)�ķ�����̎��������������MCU���Ձ��Ĕ�(sh��)��(j��)ָ���M(j��n)�з�����������ָ��Ҫ���M(j��n)������(y��ng)����������A��D�ɘӁ��Ĕ�(sh��)��(j��)������(sh��)��(j��)�M(j��n)��̎�����惦(ch��)�ȹ�����

(2)A��D���Ɔ�Ԫ����Ҫؓ(f��)؟(z��)�����ⲿA��DоƬ�Ͷ�·�_�P(gu��n)���xͨ�r(sh��)���Լ���(sh��)�F(xi��n)��A��D��Ҫ�^�̵ĺ������ƣ�����FPGA��(sh��)�F(xi��n)A��D�Ԅ�(d��ng)�ɼ��c��(sh��)��(j��)�惦(ch��)��

(3)��(sh��)�����O(ji��n)�y���Ɔ�Ԫ��ؓ(f��)؟(z��)����Ҫ�O(ji��n)ҕ�Ϳ��ƵĔ�(sh��)�����Ġ�B(t��i)��(sh��)��(j��)�IJɼ��Ϳ��������ݔ�����@һ������Ҫ��(sh��)�F(xi��n)��(sh��)����ݔ���Ŀ��ơ���(sh��)����ݔ��Ĵ惦(ch��)����(sh��)����ݔ���B(t��i)׃���R�e(�Д�ݔ��)��

(4)FPGA�ӿ�߉���Ɔ�Ԫ����FPGA��(n��i)���O(sh��)Ӌ(j��)��FPGAģ�K�c���MCU�Ľӿچ�Ԫ��ԓ������Ҫ����ͬCPU�Ľӿڣ�ʹ��(sh��)��(j��)�ɼ�ϵ�y(t��ng)���Է�����cPCI��ISA�����������B�ӡ�

3 ģ�M���ɼ��Ŀ����c����

��ģ�M���ɼ�����·�У�A��DоƬ���õ���AD��˾��AD976A����·ģ�M����ͨ�^AD438�Ķ�·�_�P(gu��n)��ݔ�뵽AD976AоƬ�ġ�

A��D�ɘӲ��ֿɷ֞飺�Ĵ����M���r(sh��)犰l(f��)��ģ�K���ɘӿ��Ơ�B(t��i)�C(j��)����(sh��)��(j��)�惦(ch��)ģ�K��

3��1 �Ĵ����M

�Ĵ����M�����O(sh��)�ã��xȡA��D�Ĺ�����B(t��i)���������ɘ��l���O(sh��)�üĴ���������ģʽ�x��Ĵ�����������B(t��i)�Ĵ�����FIFO�Д�Ĵ�����

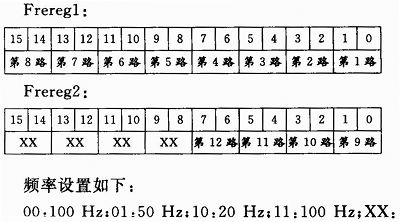

(1)�ɘ��l���O(sh��)�üĴ���Frereg1��F(xi��n)rereg2(R��W)���ɂ�(g��)16λ�Ĵ����������O(sh��)��12·A��D�IJɘ��l�ʣ���λ���x���£�

�l���O(sh��)�����£�

�鱣��λ��

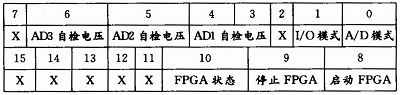

(2)����ģʽ�x��Ĵ���modereg(R��W)��176λ�Ĵ����������O(sh��)��A��D�Ĺ���ģʽ�͆���(d��ng)��ֹͣFPGA����λ�Ķ��x���£�

(3)FIFO�Д�Ĵ���(fifo_int)(R)��16λ�Ĵ������Á�ӛ�FIFO�Ġ�B(t��i)����λ���x���£�

3��2 �r(sh��)犰l(f��)��ģ�K

(1)�ѕr(sh��)犷��l��1 MHz�r(sh��)犣������B(t��i)�C(j��)�Ĺ����r(sh��)犣�

(2)����20 Hz��50 Hz��100 Hz�r(sh��)犲��Y(ji��)��Frereg��ֵ�o��12·A��D����(d��ng)�Д���̖��

3��3 �ɘӿ��Ơ�B(t��i)�C(j��)

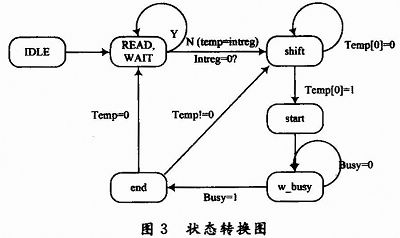

ÿ��(g��)A��D��һ��(g��)�ɘӿ��Ơ�B(t��i)�C(j��)�������Ԅ�(d��ng)����A��D�Ĕ�(sh��)��(j��)�ɼ������B(t��i)�D(zhu��n)�Q�D��D3��ʾ��

IDLE�����e��B(t��i)��

READ��temp=intreg���M(j��n)����һ��B(t��i)

WAIT���ȴ��Д࣬����Д�Ĵ���(intreg)����0���M(j��n)����һ��B(t��i)����t����READ��

SHIFT������(j��)temp[0]��ֵ�M(j��n)����һ����������temp[0]=0�ttemp>>1��ͬ�r(sh��)ͨ��Ӌ(j��)��(sh��)��(counter)��1����temp[0]=1���t����(j��)counter��ֵ�o��ͨ���x����̖���M(j��n)����һ��B(t��i)��

START���l(f��)��RC=0��̖���M(j��n)����һ��B(t��i)��

W_BLISY��RC=1���ȴ�A��D�D(zhu��n)�Q�Y(ji��)����̖������Y(ji��)����temp>>1���l(f��)����FIFO��̖���M(j��n)����һ��B(t��i)��

END���oЧFIFO����̖����temp=0�������џo�Д࣬coutnter=0���M(j��n)��WAIT����t��counter+1���M(j��n)��SHIFT��

3��4 ��(sh��)��(j��)�惦(ch��)ģ�K

���ڴ惦(ch��)A��D�D(zhu��n)�Q�Y(ji��)��������ÿ·A��D��һ��(g��)FIFO��

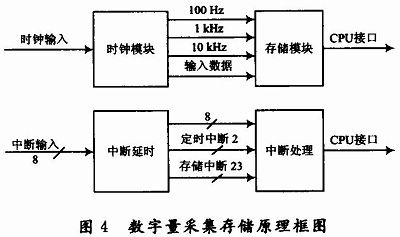

4 ��(sh��)�ֲɼ�ģ�K

��(sh��)�ֲɼ�ģ�K��Ҫ��ɔ�(sh��)����ݔ��IJɼ��c�惦(ch��)���Д���̖��B(t��i)�R�e���ܡ���ԭ��D��D4��ʾ��

5 �Y(ji��)Փ

���������һ�N����FPGA���g(sh��)�Ķ�·ģ�M������(sh��)�����ɼ��c̎��ϵ�y(t��ng)���O(sh��)Ӌ(j��)������(y��ng)�����Ӳ���·��ϵ�y(t��ng)̎��ܛ�����ڷ���;C���{(di��o)ԇ�ɹ��Ļ��A(ch��)�ϣ���ϵ�y(t��ng)�ɹ�����ij���c(di��n)�A(y��)���(xi��ng)Ŀ�Ŀ���ϵ�y(t��ng)ԇ�(y��n)�С�ԇ�(y��n)�Y(ji��)����������ϵ�y(t��ng)�ɹ�������ˌ���·ģ�M������(sh��)�����IJɼ�̎���΄�(w��)��

���P(gu��n)��x:

- ...2012/03/31 10:53������FPGA�����l�x�����O(sh��)Ӌ(j��)

- ...2011/12/02 16:57������FPGAֱ�����ДU(ku��)�lϵ�y(t��ng)���O(sh��)Ӌ(j��)

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��Ђ�ݔϵ�y(t��ng)���O(sh��)Ӌ(j��)�c��(sh��)�F(xi��n)

- ...2011/11/07 15:10������FPGA��ͨ�î����հl(f��)���O(sh��)Ӌ(j��)

- ...2011/11/07 15:10������FPGA���h(yu��n)���x�y������(sh��)��ϵ�y(t��ng)�O(sh��)Ӌ(j��)

- ...2011/10/31 16:02������FPGA�Ľ�ͨ��ϵ�y(t��ng)�����O(sh��)Ӌ(j��)

- ...���D��Ԕ����܇�x���屳���܇Ҏ(gu��)����ȫ�O(sh��)Ӌ(j��)Ҫ��

- ...��ʹ���а�ȫ���ϵ��W��惦(ch��)��(g��u)����ȫ����܇ϵ�y(t��ng)

- ...������ƫ�ò�־��Ԃ��������^���M(j��n)չ�͑�(y��ng)��

- ...�����¿�˹�y�uijƷ�����ܲ����������C(j��)����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�(�m(x��))

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�

- ...���{(l��n)��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^(q��)�e

- ...��IoT�W(w��ng)�P(gu��n)ƽ�_�c��(y��ng)��

- ...������(qi��ng)��ARM DesignStart��ͨ���ƻ�SoC���^�졢�^���L(f��ng)�U(xi��n)֮·

- ...����(sh��)�w�����D(zhu��n)��O2O���}��(ch��)���������ܻ�ˮƽ�ĺ�������

- ...���N܇��LED�(q��)��(d��ng)�����ı��^

- ...���{(l��n)���䌦�ڶ�ƪ��������ɷ���

- ...��������A�Ƴ��I(l��ng)�ȵğo����(sh��)��(j��)�ɼ���Q����

- ...����ɭ���댧(d��o)�w����Ј�څ�ݵğo����늷���

- ...����ɭ���댧(d��o)�w�����܇�����O(sh��)Ӌ(j��)څ�ݵĽ�Q����

- ...�� ��о��(chu��ng)�����ø�Уδ����܇�˙C(j��)�����O(sh��)Ӌ(j��)��ِ��(b��o)����ʽ����(d��ng)

- ...�� ̽�صڶ����l(w��i)�{(l��n)ɽ������(chu��ng)�¡�������ԇ�(y��n)���g(sh��)Փ����

- ...�� ��2018�Ї��댧(d��o)�w���B(t��i)朴��(hu��)���ڽ��Kʡ�����e��

- ...�� �����}��Ҏ(gu��)����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�(chu��ng)������ܵ�����

- ...�� �ⷨ�댧(d��o)�w��ST����Cinemo��Valens��CES 2018չ��(li��n)����ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a(ch��n)�I(y��)��(chu��ng)�°l(f��)չ�߷�Փ�������ھ����_

- ...�� ����늙C(j��)��(qi��ng)�ݳ���PCIM����2017չ

- ...�� GPGPU���a(ch��n)������Ї�оƬ�a(ch��n)�I(y��)�Ŀհ؎�

- ...�� ��(li��n)�W(w��ng)�a(ch��n)Ʒ�O(sh��)Ӌ(j��)��Wi-Fi�B�ӵ��Ă�(g��)�P(gu��n)�I����

- ...�� �������Ї�MEMS���܂������a(ch��n)�I(y��)�l(f��)չ���(hu��)�����ڰ������_�Ļ

- ...�� IAIC���(xi��ng)ِ���[���Ї�о����(y��ng)�Ä�(chu��ng)�£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g(sh��)

- ...�� ����(g��)�Ј��������L�Ƅ�(d��ng)Molex�ӏ�(qi��ng)��܇�I(l��ng)��İl(f��)չ

- ...�� �Ї��Gɫ����(li��n)�˳������(hu��)���_�ڼ� ���a(ch��n)�W(xu��)���ù�̽�Gɫ�l(f��)չ��ģʽ

- ...�� Efinix® ȫ���(q��)��(d��ng)AI߅��Ӌ(j��)�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r(sh��)���a(ch��n)Ʒ�U(ku��)չ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M(j��n)����(hu��)�����I(l��ng)�ǻ�������

- ...�� ��늮a(ch��n)Ʒ�_�l(f��)���yԇ��ӑ��(hu��)��������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧(d��o)�w�I(l��ng)�� ����弉�ȳ��ͷ��b�ṩ���W(xu��)���Ƴ̡�Ϳ�������⑪(y��ng)�õ����a(ch��n)�O(sh��)���Q����

- ...�� ������ABITRODE��(d��ng)��늳yԇϵ�y(t��ng)���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y(t��ng)�И�(bi��o)��������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ(f��)�dϵ�y(t��ng)�ɹ����������؈

- ...�� ������A���H��늄�(d��ng)��܇���P(gu��n)�I�����y�u��ӑ��(hu��)�����[���M(j��n)�y�u���g(sh��)

- ...�� ��(sh��)��(j��)�ɼ��K��ϵ�y(t��ng)�O(sh��)��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|(zh��)�J(r��n)�C����܇ϵ�Юa(ch��n)ƷӋ(j��)��

- ...�� ���`˼® �����U(ku��)������� ⁽�ϵ��™ FPGA �a(ch��n)Ʒ ⁽�ϵ�Юa(ch��n)Ʒ�U(ku��)�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ��(ji��)�c(di��n)��Ƭ

- ...�� TI��2019��ȫ����W(xu��)������O(sh��)Ӌ(j��)��ِ�C��(ji��ng)��Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C(j��)�@��ȫ���ׂ�(g��)��܇��ȫ�����Եȼ�(ASIL) ��D���J(r��n)�C

- ...�� ���R��܇�x��BlackBerry������һ����܇