����FPGA�Ľ�ͨ��ϵ�y�����OӋ

ժҪ�����ˌ���ͨ��ϵ�y�M�о��_���ƣ�����FPGA���壬��Quartus��ܛ���h���£��քe���F�}�_�l��ģ�K����B���rģ�K����ͨ���@ʾģ�K���r�g�@ʾģ�K���M�з��挍��Ӳ�����d���@�õĜyԇ�Y���M���OӋҪ�����ڲ�����EDA���g��ʹ����ϵ�y�OӋ��Ч���@����ߡ�

�P�I�~��FPGA��Quartus��ͨ��������ϵ�y�OӋ

Ŀǰ��ͨ��V�������ڵ�·��ͨ���O�С������OӋһ��ʮ��·�ڽ�ͨ�������·��Ҫ��|�����ϱ��ɗl�ɵ��ļt���G���S��ͨ����Ҫ��ѭ�h׃�������Ե�Ӌ�r��ʽָʾ�ɵ�ͨ�л��ֹ�ľS�֕r�g����Quartus��ܛ���h�����OӋ�����棬����FPGA�����ό��F���OӋ�·�Ĺ��ܡ�

1 ϵ�y����

1��1 �OӋ˼��

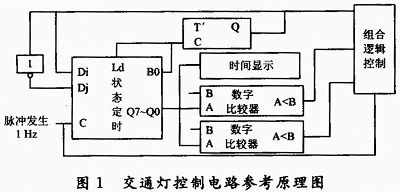

����FPGA�Ľ�ͨ��ϵ�y�����OӋ����4��ģ�K���քe���}�_�l������B���r����ͨ���W�q�Ŀ��ơ��W�q�r�g�Ŀ��ƣ�����ԭ����D1��ʾ��

1��2 ���w������r

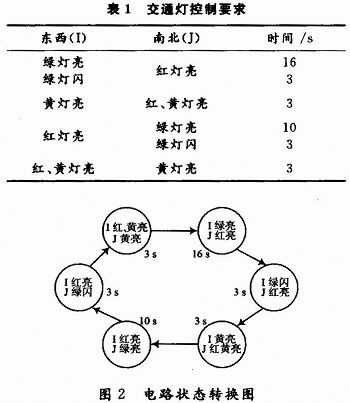

��ͨ������Ҫ�����1��ʾ��

ԓ�OӋ�Ľ�ͨ�����Ʒ֞�6����B�����ڸ���B���m�r�g��ͬ�������·�ĺ��Ŀ��Ʋ����Ǡ�B�C�Ͷ��r������B�C�ڶ��r���|�l��������ѭ�h����B�a����6������һ����Ҏ��׃����׃����r��D2��ʾ��

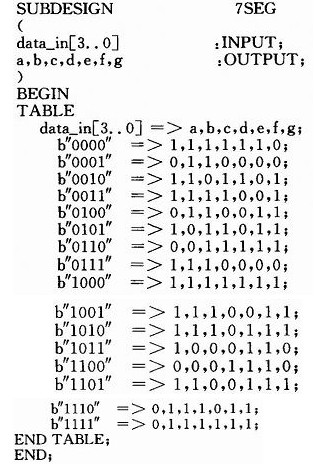

ϵ�y�}�_��FPGA�_�l�徧���^���l�·���F����B���r��74190����ʮ�M��Ӌ������T’�|�l�����F��ֻҪ�Ô����������D��̖��λ���Ϳ���ʹ�·�ږ|��(I)���ϱ�(J)�ɂ����Ơ�B�g���D���t���S���G�����W�q��7485���ֱ��^���ͽM��߉���ƣ�����7485���ֱ��^�����ڱ��^Ӌ������ǰ���m��B������Ҫ�Ġ�Bȫ���r�g��������������׃�����M��߉������AHDL�ļ�������ֵ�팍�F���r�g�@ʾ��AHDL�ļ�������ֵ�팍�F��ݔ�����_��߉���߶��g�a�·���ܵõ����_�ĕr�g�@ʾ��

1��3 �����ܵĽM��

�����·���Է֞�4�֣������}�_�l������B���r���r�g�@ʾ�͔��ֱ��^һ�M��߉���ơ�

1��3��1 �}�_�l��

�}�_�l����������ϵ�y�ṩ�ӣ���ݔ��˷���oFPGA�����PIN55���_���t���Ɍ����Ϯa���l�ʞ�10 MHz��ݔ���}�_����7Ƭ7490��ÿһ��������10���l�·��ʹ�l�ʏ�10 MHz���͞�1Hz��

1��3��2 ��B���r

��B���r�����A��BCD�a��ֵ��74190�����F�����ɜpӋ��������ԭ�t�ǣ���λӋ������ȫ0��B׃���^��aֵ��B�r��ʹ��λӋ�����p1������ʽ�֞鮐����ͬ���ɷN�����IJ�ȡ���Ǯ�������ʽ������λӋ���������̖���Ƹ�λӋ������ӛ���}�_ݔ��ˡ��ɸ���Ӌ�����ĕr��|�l��ʽ���ڵ�λӋ������B�a��ȫ“0”׃���^��aֵ��˲�g�����λӋ�����ṩ��Ч��Ӌ���}�_߅�ء����w�����nj���Ƭλ�������̖RCON�˿ڽӵ���Ƭλ��Ӌ���}�_CLK�����F��λBCD�a���Ô������D�ͽ�λ��ʹϵ�y��ʾ�Ĕ�������22��16֮�gѭ�h��

74190�����f����

(1)GN��Ӌ����ʹ�ܿ��ƶˣ����ƽ��Ч����GN����ƽ�r����ֹӋ����

(2)DNUP��Ӌ����ʽ���ƣ��Ӹ��ƽ��pӋ�����ӵ��ƽ���Ӌ����

(3)LDN�鮐���A�Ô����ơ���LDN����ƽ�r��Ӌ������BQD��QC��QB��QA�քe����D��C��B��A��

(4)Ӌ����λ���ɸ���������QD��QC��QB��QA��QD���^��λMSB��QA���^��λLSB��

(5)Ӌ���}�_CLK��������Ч��

(6)��Ӌ����ݔ��QDQCQBQA��ʮ�M�Ƽ�Ӌ�����^���B�a“1001”���pӋ�����^С��B�aȫ“0”�r���Oֵ��B�aָʾMAX��MINݔ������ƽ��

(7)���Oֵ��B�aָʾMAX��MIN����ƽ��CLK����ƽ�r�������̖RCON����ƽ����RCON�cӋ���}�_ͬ����

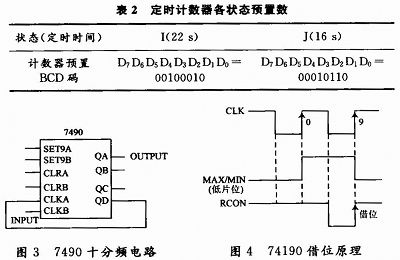

ϵ�yӛ���}�_��1 Hz�r�����2��ʾ����I��B(�|�����Ơ�B)�Ķ��r�r�g��22 s��Ӌ������ԓ���A��22��BCD�a��ͬ����J��B(�ϱ����Ơ�B)֮ǰ��ԓ�A��16��BCD�a��

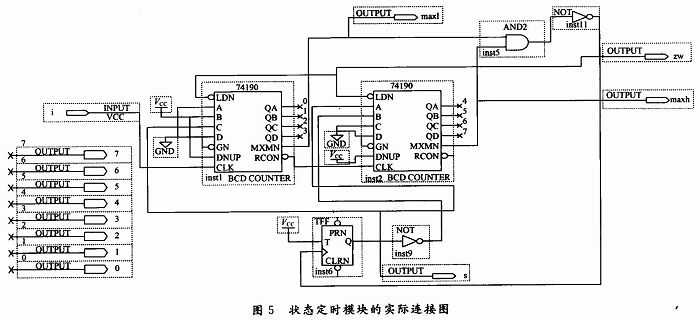

��BӋ�r�·�Ƀ�Ƭ74190�����ɣ�����22��16�Է��D���·����Ҫ��Q�ĺ��Ć��}�����Ô������D�ͽ�λ������74190оƬ�����c���ɷ����䌍�Fԭ����D4��ʾ��ͨ�^�����̖RCON�������،��F��λ��ʹ�Ô����܉��20��19����λ��ʮλ��λ������^�ɡ�

�Ô��ͷ��D֮�g���Ⱥ��Pϵ��������Ô����D�����3��ʾ�������ɂ�BCD�a��λ���c����֪����D7D6D3D0λ����1��D1λ����0����D5D4D2λ��ͬ����D5��D5D4D2λ�ɠ�B�ƽS�����ƣ�����I��B�r��Ӌ�������A�õĔ���D5=0��D4=D2=1������J��B�r��Ӌ�������A�õĔ���D5=1��D4=D2=0������74190�Ĺ��ܣ���2Ƭ74190��MAX��MIN������ͨ�^�c���T���քe�B�ڸ�λ�͵�λ��LDN�Ô��ˣ�ͨ�^������֪����Ӌ������01�p��00�r�ߵ�λ��MAX��MIN������ƽ�����^�c���T�Ժ����ƽ��74190���Ô������Ô�ֵ�ɠ�BS��Q����S����LDN����̖��

�^һ��T’�|�l���Q���ģ���LDN��̖ÿ�Ô�һ�Σ�S���D1�Σ��Ķ��^��16��22��B�����@���Y�����ɷքe�Ô�16��22��ʹ�䌍�F�Է��D��

�D5���B���rģ�K�Č��H�B�ӈD��

1��3��3 �r�g�@ʾ

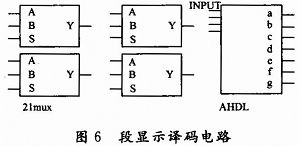

�r�g�@ʾҪ�õ�7���@ʾ�g�a�·�������ǃ�λBCD�a�����ö��xһ�����x�������x���S��һ���l�ʺܸߵķ���(��1 kHz)���������^����ݔ����1 Hz�}�_����AHDLģ�K��ݔ�룬�������_�@ʾ�r�g��

![]()

�����_�@ʾ�r�g����AHDL�ļ��Ծ��g�a��ֵ�����£�

1��3��4 ���ֱ��^һ�M��߉����

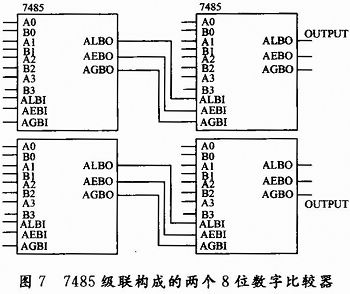

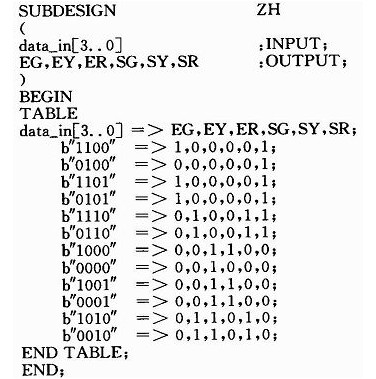

ԓģ�K����B���rģ�Kݔ���ĕr�g�c�r�g���c�M�б��^���Ķ��_���·̎��22 s����16 s�ľ��w��ij����B���ɱ�1��֪���|��(I)���ϱ�(J)�Ŀ��Ơ�B����3���A�εĿ���߉���քe����3���r�g�Σ�1��3 s��4��6 s�ʹ���6 s����ˣ����Ô��ֱ��^���M�б��^���_�����rֵС��4 s�����6 s��������D7��ʾ������4Ƭ7485���ֱ��^�����Ƀɼ�������һ���ɠ�B���rģ�K��ݔ���c4�����M��0100���^����һ���ɠ�B���rģ�K��ݔ���c6�����M��0110���^��

�����M��߉��ֵ��������B��̖S���ɂ����ֱ��^����ݔ��Y1��Y2��1 Hz�}�_����ݔ�룬�������Ġ�B����ݔ�����Ķ�����߉�Pϵ�ó������r�g�·�Ġ�B�����Ƽt���S���G��̎�ڲ�ͬ�Ġ�B��S�Д��·̎��22 s��B߀��16 s��B��Y1��Y2�^�֖|�����ϱ������A�Π�B��1 Hz�}�_���F�G���W�q��

2 �·�ĽM���c�{ԇ

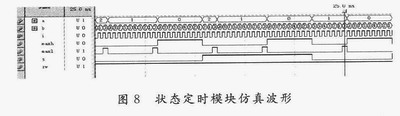

����Quartus��ܛ���OӋ����ģ�K�����M�з��档�_�J�Y�������d��FPGA�����У��M��������Ӳ���{ԇ���{ԇ�Y���c����Y����һ�¡��D8����沨�Σ�ϵ�y�����Ҫ�{�����^�̣�����·��������ǰ�؏���22s�Ġ�B��

���P��x:

- ...2012/03/31 10:53������FPGA�����l�x�����OӋ

- ...2011/12/02 16:57������FPGAֱ�����ДU�lϵ�y���OӋ

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��Ђ�ݔϵ�y���OӋ�c���F

- ...2011/11/07 15:10������FPGA��ͨ�î����հl���OӋ

- ...2011/11/07 15:10������FPGA���h���x�y��������ϵ�y�OӋ

- ...2011/10/31 16:02������FPGA�Ĕ����ɼ�ϵ�y�OӋ

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇