TMS320C61416控制FPGA數據加載設計

目前實現加載的方法通常有兩種:一種是用專用Cable通過JTAG口進行數據加載,另一種是外掛與該FPGA廠商配套的PROM芯片。前者需要在PC機上運行專用的加載軟件,直接下載到FPGA片內,所以掉電數據仍然會丟失,只適用于FPGA調試階段而不能應用于工業現場的數據加載。后者雖然可以解決數據丟失問題,但這種專用芯片成本較高,供貨周期也較長(一般大于2個月),使FPGA產品的開發時間受到很大約束。根據FPGA芯片加載時序分析,本文提出了采用通過市面上常見的Flash ROM芯片替代專用PROM的方式,通過DSP的外部高速總線進行FPGA加載;既節約了系統成本,也能達到FPGA上電迅速加載的目的;特別適用于在FPGA調試后期,待固化程序的階段。下面以兩片Xilinx公司Virtex-4系列XC4VLX60芯片為例,詳細介紹采用TI公司的TMS320C61416 DSP控制FPGA芯片數據加載的軟硬件設計。

1 Xilinx FPGA配置原理

Virtex-4系列的FPGA芯片外部配置引腳MODE PIN(M0、M1、M2),有5種配置模式,如表1所列。

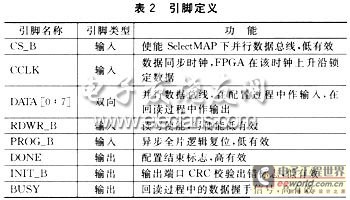

FPGA在Slave SelectMAP方式下,共用了表2所列的15個配置引腳。

1.1 配置流程

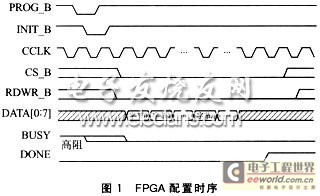

FPGA加載時序如圖1所示。各配置信號必須滿足其時序關系,否則配置工作無法正常完成。

圖1中,Slave SelelctMAP加載主要包括以下3個步驟:

①啟動和初始化。FPGA上電正常后,通過PROG_B引腳低脈沖進行FPGA異步復位,使得FPGA內部邏輯清零。其次PROG_B上拉高,停止外部復位,INIT_B引腳會在TPOR時間段內自動產生一個由低到高的跳變,指示FPGA內部初始化完成,可以進行數據下載;同時FPGA在INIT_B的上升沿采樣其模式引腳MODE PIN,決定其模式配置。

②比特流加載。INIT_B信號變高后,不需要額外的等待時間,Virtex器件就可以立即開始數據的配置。比特流數據在外部CCLK信號上升沿按字節方式置入。該過程包括同步初始化字、器件ID號校驗、加載配置數據幀、CRC校驗4個部分。

③STARTUP啟動。在成功校驗CRC碼位后,比特流命令使得FPGA進入STARTUP狀態。它是由8相狀態機實現的。中間包括等待DCM鎖相、DCI匹配等幾個狀態,較后FPGA釋放外部DONE引腳,對外輸出高阻態,由外部上拉高,指示FPGA加載成功。

1.2 文件生成

ISE生成數據文件主要有3種:BIT文件,由二進制格式進行表征邏輯設計,包括文件頭和配置數據,主要用于JTAG下載電纜模式;MCS文件,為外部PROM燒寫生成的下載文件,ASCII碼,與前者不同的是它含有在PROM中的數據地址和校驗值;BIN文件格式,由二進制表示,完全由配置數據組成,不需要作其他的提取和進制轉換,只是配置前的Byte-Swapped是在CPLD中實現的。本設計采用的是BIN文件格式。

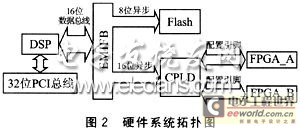

2 硬件實現

系統采用2片Xilinx Virtex-4系列的600萬門的FPGA XC4VLX60。主MCU是TI公司高性能定點處理器TMS320C6416,對外有2個EMIF總線接口,分別是64位寬EMIFA和16位寬EMIFB。EMIFB上掛有8位8MB的Flash和16位CPLD:Flash做2片FPGA的BIN文件保存,之前由仿真器燒寫;CPLD用于2片FPGA地址譯碼和DSP與FPGA配置部分的邏輯接口。整個數據流程是在DSP上電啟動后,Bootloader自行引導用戶程序運行。該程序負責由EMIFB總線搬移Flash空間中BIN文件,通過CPLD分別對2片FPGA進行配置加載。硬件系統拓撲圖如圖2所示。

3 軟件設計

軟件包括3部分:引導Bootloader代碼,加載FPGA用戶程序以及接口部分的CPLD Verilog代碼。

3.1 DSP Bootloader

本系統中目標板處于FPGA調試后期,需要固化其加載程序。整板上電后,要求脫離仿真器自行加載FPGA,因此這里采用DSP的EMIF BooT方式。它是由DSP上電復位后,以默認ROM時序通過EDMA自行搬移BCE1的ROM空間前1 KB內容到片內,在其0x0地址開始運行。

一般由C編寫的程序代碼長度都遠大于1 KB,如果只是純粹由DSP搬移Flash前1 KB空間,這樣便會丟失數據,程序無法正常運行。這里采用由匯編語言寫的一個兩次搬移的Bootloader程序,來引導較大的用戶程序。使用匯編語言是因為其代碼效率高,代碼長度短(本系統中只有256字節)。兩次搬移是因為第一次DSP自行搬移后的Bootloader會占用片內的0x0地址前1 KB空間,與下一步的用戶程序0x0地址拷貝沖突(中斷向量表必須放在0x0地址,否則會丟失中斷跳轉的絕對地址),且運行中的Bootloader不能覆蓋自身。所以把拷貝用戶程序的那部分代碼放在片內較底端運行,騰出了用戶空間的0x0地址。較后整體拷貝結束后,Bootloader再跳轉到用戶程序入口地址c_int00運行。

關鍵字:FPGA TMS320C61416 數據加載

3.2 用戶程序和CPLD程序

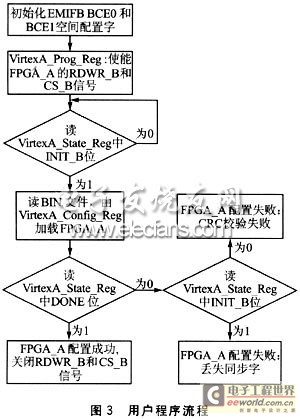

本系統中2片FPGA加載的原理一樣。為避免繁瑣,這里以1片FPGA_A為例來作介紹。

CPLD在系統中負責2項工作。

①映射DSP端Flash分頁寄存器:控制Flash的高3位地址線,分8頁,每頁1 MB空間。

②映射DSP端2片FPGA的加載寄存器:

a.配置寄存器FpgaA(B)_config_Reg[8:O]。負責配置數據和時鐘,高8位為Byte-Swapped前的數據位,輸出到配

置引腳時進行字節交換,較低位為CCLK位。

b.控制寄存器FpgaA(B)_Prog_Reg[2:O]。負責外部控制引腳,分別為CS_B、RDWR_B和PROG_B。

c.狀態寄存器FpgaA(B)_State_Reg[2:0]。負責回讀配置中的握手信號,分別為BUSY、DONE和INIT_B。

由Bootloader引導的用戶程序由C語言開發,在CCS下調試通過。它主要實現Flash翻頁,把之前燒寫在Flash中的BIN文件,通過上述CPLD中3個加載寄存器對FPGA進行上電配置。具體流程如圖3所示。

當前FPGA配置時鐘CCLK是在用戶程序中通過DSP寫命令產生的,即寫FpgaA(B)_Config_Reg的CCLK位高低電平;同時8位配置數據也連續寫2次,由CPLD鎖存到FPGA總線上,便能充分保證圖1中該有效數據在CCLK上升沿上被鎖。

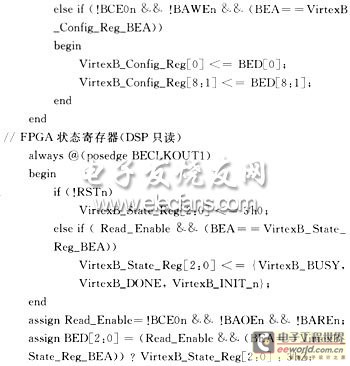

以下是CPLD中動態加載部分的Verilog代碼:

//FPGA控制寄存器(DSP只寫)

結 語

該系統已成功用于某公司一款軟件無線電平臺中,通過反復軟硬件調試,現已投放市場。此平臺不僅可以實現上述提到的上電Flash自行加載FPGA的目的,還可在其配置完以后通過主機端對FPGA實現動態加載,充分滿足了軟件無線電中可重構化、實時靈活的指導思想。

相關閱讀:

- ...2015/06/24 20:26·TMS320C6678 存儲器訪問性能 (下)

- ...2015/06/18 16:45·TMS320C6678 存儲器訪問性能 (上)

- ...2012/02/03 11:33·基于TMS320X2812的高精度轉角測量系統設計

- ...2011/12/02 16:57·基于TMS320LF2407的天然氣發動機控制系統設計

- ...2011/11/11 10:37·TMS320C5409實現JPEG圖像壓縮系統設計

- ...2011/11/07 10:13·基于TMS320F2812的光標閱讀機系統

- ...· Efinix® 全力驅動AI邊緣計算,成功推出Trion™ T20 FPGA樣品, 同時將產品擴展到二十萬邏輯單元的T200 FPGA

- ...· 英飛凌亮相進博會,引領智慧新生活

- ...· 三電產品開發及測試研討會北汽新能源專場成功舉行

- ...· Manz亞智科技跨入半導體領域 為面板級扇出型封裝提供化學濕制程、涂布及激光應用等生產設備解決方案

- ...· 中電瑞華BITRODE動力電池測試系統順利交付北汽新能源

- ...· 中電瑞華FTF系列電池測試系統中標北京新能源汽車股份有限公司

- ...· 中電瑞華大功率高壓能源反饋式負載系統成功交付中電熊貓

- ...· 中電瑞華國際在電動汽車及關鍵部件測評研討會上演繹先進測評技術