基于FPGA的高速FIR數(shù)字濾波器的設(shè)計(jì)

1 引 言

目前FIR濾波器的實(shí)現(xiàn)方法主要有3種:利用單片通用數(shù)字濾波器集成電路、DSP器件和可編程邏輯器件實(shí)現(xiàn)。單片通用數(shù)字濾波器使用方便,但由于字長(zhǎng)和階數(shù)的規(guī)格較少,不能完全滿足實(shí)際需要。使用DSP器件實(shí)現(xiàn)雖然簡(jiǎn)單,但由于程序順序執(zhí)行,執(zhí)行速度必然不快。

FPGA有著規(guī)整的內(nèi)部邏輯陣列和豐富的連線資源,特別適合于數(shù)字信號(hào)處理任務(wù),相對(duì)于串行運(yùn)算為主導(dǎo)的通用DSP芯片來(lái)說(shuō),其并行性和可擴(kuò)展性更好。但長(zhǎng)期以來(lái),F(xiàn)PGA一直被用于系統(tǒng)邏輯或時(shí)序控制上,很少有信號(hào)處理方面的應(yīng)用,其原因主要是因?yàn)樵贔PGA中缺乏實(shí)現(xiàn)乘法運(yùn)算的有效結(jié)構(gòu)。本文利用FPGA乘累加的快速算法,可以設(shè)計(jì)出高速的FIR數(shù)字濾波器,使FPGA在數(shù)字信號(hào)處理方面有了長(zhǎng)足的發(fā)展。

2 Matlab設(shè)計(jì)濾波器參數(shù)

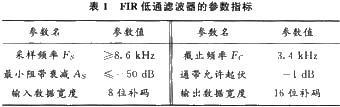

以表1的濾波器參數(shù)為例,分析設(shè)計(jì)高速FIR數(shù)字濾波器的方法。

利用Matlab為設(shè)計(jì)FIR濾波器提供的工具箱,選擇濾波器類型為低通FIR,設(shè)計(jì)方法為窗口法,階數(shù)為16,窗口類型為Hamming,Beta為0.5,F(xiàn)s為8.6 kHz,F(xiàn)C為3.4 kHz,導(dǎo)出的濾波器系數(shù)如下:

3 快速FIR濾波器算法的基本原理

(1) 分布式算法

分布式算法在完成乘加功能時(shí)是通過(guò)將各輸入數(shù)據(jù)每一對(duì)應(yīng)位產(chǎn)生的部分積預(yù)先相加形成相應(yīng)的部分積,然后再對(duì)各部分積進(jìn)行累加得到較終結(jié)果。

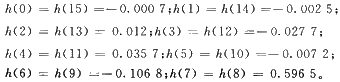

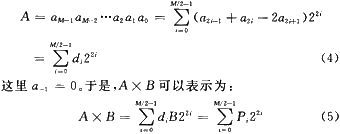

對(duì)于一個(gè)N(N為偶數(shù))階線性相位FIR數(shù)字濾波器,輸出可由式(1)表示:

(2) 乘法器設(shè)計(jì)

高性能乘法器是實(shí)現(xiàn)高性能的FIR運(yùn)算的關(guān)鍵,分析乘法器的運(yùn)算過(guò)程,可以分解為部分積的產(chǎn)生和部分積的相加兩個(gè)步驟。部分積的產(chǎn)生非常簡(jiǎn)單,實(shí)現(xiàn)速度較快,而部分積相加的過(guò)程是多個(gè)二進(jìn)制數(shù)相加的加法問(wèn)題,實(shí)現(xiàn)速度通常較慢。解決乘法器速度問(wèn)題,需要分別從這兩個(gè)方面入手,減小部分積的個(gè)數(shù),提高部分積相加運(yùn)算的速度。

3.1 Booth算法

Booth算法針對(duì)二進(jìn)制補(bǔ)碼表示的符號(hào)數(shù)之間的相乘,即可以同時(shí)處理二進(jìn)制正數(shù)/負(fù)數(shù)的乘法運(yùn)算。Booth算法乘法器可以減少乘法運(yùn)算部分積個(gè)數(shù),提高乘法運(yùn)算的速度。

下面討論一個(gè)M b×N b乘法器基本單元的設(shè)計(jì)。設(shè)乘數(shù)為A,為M比特符號(hào)數(shù),2的補(bǔ)碼表示,相應(yīng)各比特位的值為ai(i=0,1,…,M-2,M-1),用比特串可表示為:

A=aN-1aN-2…a2a1a0 (2)

設(shè)被乘數(shù)為B,為N比特符號(hào)數(shù),2的補(bǔ)碼表示,相應(yīng)各比特位的值為bi(i=0,1,…,N-2,N-1),用比特串可表示為:

B=bN-1bN-2…b2b1b0 (3)

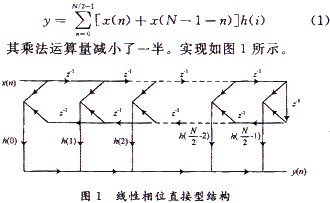

MacSoley提出了一種改進(jìn)Booth算法,將需要相加的部分積數(shù)減少為一半,大大提高了乘法速度。改進(jìn)Booth算法對(duì)乘數(shù)A中相鄰3個(gè)比特進(jìn)行編碼,符號(hào)數(shù)A可表示為:

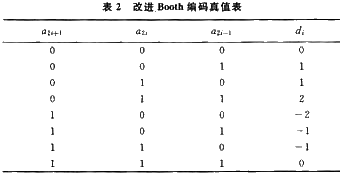

改進(jìn)Booth算法根據(jù)用2的補(bǔ)碼表示的乘數(shù)比特圖案給出編碼值di,其真值表如表2所示。

因此,應(yīng)用改進(jìn)Booth算法的乘法器運(yùn)算過(guò)程仍然包括Booth編碼過(guò)程,即部分積產(chǎn)生過(guò)程和部分積相加過(guò)程。所不同的是,其產(chǎn)生的部分積個(gè)數(shù)減少到原來(lái)的一半。

3.2 Wallace樹加法

在采用改進(jìn)Booth算法將部分積數(shù)目減少為原來(lái)的一半之后,乘法運(yùn)算的主要問(wèn)題就是處理多個(gè)多比特二進(jìn)制操作數(shù)相加的問(wèn)題。較直觀的算法是將多個(gè)部分積逐一累加,但效率很低,運(yùn)算時(shí)延巨大。

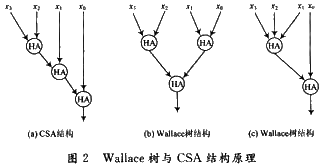

Wallace在1964年提出采用樹形結(jié)構(gòu)減少多個(gè)數(shù)累加次數(shù)的方法,稱為Wallace樹結(jié)構(gòu)加法器。Wallace樹充分利用全加器3-2壓縮的特性,隨時(shí)將可利用的所有輸入和中間結(jié)果及時(shí)并行計(jì)算,因而可以將N個(gè)部分積的累加次數(shù)從N-1次減少到log2N次,大大節(jié)省了計(jì)算時(shí)延。如圖2所示為Wallace樹結(jié)構(gòu)與CSA結(jié)構(gòu)的對(duì)照,其結(jié)構(gòu)的關(guān)鍵特征在于利用不規(guī)則的樹形結(jié)構(gòu)對(duì)所有準(zhǔn)備好輸人數(shù)據(jù)的運(yùn)算及時(shí)并行處理。

Wallace樹結(jié)構(gòu)一般用于設(shè)計(jì)高速乘法器,其顯著優(yōu)點(diǎn)是速度快,尤其對(duì)處理多個(gè)數(shù)相加的情況具有相當(dāng)?shù)膬?yōu)越性,缺點(diǎn)是其邏輯結(jié)構(gòu)形式不規(guī)整,在VLSI設(shè)計(jì)中對(duì)布局布線的影響較大。

3.3 進(jìn)位的快速傳遞

考慮到提高兩個(gè)多比特操作數(shù)相加運(yùn)算的速度,關(guān)鍵在于解決進(jìn)位傳遞時(shí)延較大的問(wèn)題。采用以犧牲硬件資源面積換取速度的方式,以獨(dú)立的邏輯結(jié)構(gòu)單獨(dú)計(jì)算各個(gè)加法位需要的進(jìn)位輸入以及產(chǎn)生的進(jìn)位輸出,提高進(jìn)位傳遞的速度,從而提高加法運(yùn)算速度。

3.3.1 四位超前進(jìn)位加法器的設(shè)計(jì)

兩個(gè)加數(shù)分別為A3A2A1A0,B3B2BB1B0,C-1為低位進(jìn)位。令兩個(gè)輔助變量分別為G3G2G1G0和P3P2P1P0:Gi=Ai&Bi,Pi=Ai+Bi。G和P可用與門、或門實(shí)現(xiàn)。

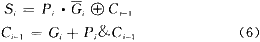

一位全加器的邏輯表達(dá)式可化為:

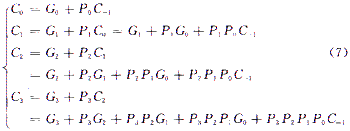

利用上述關(guān)系,一個(gè)4比特加法器的進(jìn)位計(jì)算就變化為下式:

由式(7)可以看出每一個(gè)進(jìn)位的計(jì)算都直接依賴于整個(gè)加法器的較初輸入,而不需要等待相鄰低位的進(jìn)位傳遞。理論上,每一個(gè)進(jìn)位的計(jì)算都只需要3個(gè)門延遲時(shí)間,即同時(shí)產(chǎn)生G[i],P[i]的與門以及或門,輸入為G[i],P[i],C-1的與門,以及較終的或門。同樣道理,理論上較終結(jié)果sum的得到只需要5個(gè)門延遲時(shí)間。

實(shí)際上,當(dāng)加數(shù)位數(shù)較大時(shí),輸入需要驅(qū)動(dòng)的門數(shù)較多,其VLSI實(shí)現(xiàn)的輸出時(shí)延增加很多,考慮互聯(lián)線延時(shí)的情況將會(huì)更加糟糕。因此,通常在芯片實(shí)現(xiàn)中設(shè)計(jì)位數(shù)較少的超前進(jìn)位加法器結(jié)構(gòu),而后以此為基本結(jié)構(gòu)構(gòu)造位數(shù)較大的加法器。

3.3.2 進(jìn)位選擇加法器結(jié)構(gòu)

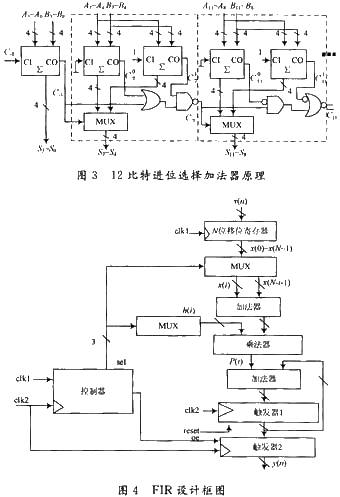

實(shí)際上,超前進(jìn)位加法器只是提高了進(jìn)位傳遞的速度,其計(jì)算過(guò)程與行波進(jìn)位加法器同樣需要等待進(jìn)位傳遞的完成。借鑒并行計(jì)算的思想,人們提出了進(jìn)位選擇加法器結(jié)構(gòu),其算法的實(shí)質(zhì)是增加硬件面積換取速度性能的提高。利用二進(jìn)制加法的特點(diǎn),進(jìn)位或者為邏輯1,或者為邏輯0,二者必居其一。將進(jìn)位鏈較長(zhǎng)的加法器分為M塊分別進(jìn)行加法計(jì)算,對(duì)除去包含較低位計(jì)算的M-1塊加法結(jié)構(gòu)復(fù)制兩份,其進(jìn)位輸入分別預(yù)定為邏輯1和邏輯0,于是M塊加法器可以同時(shí)并行進(jìn)行各自的加法運(yùn)算,然后根據(jù)各自相鄰低位加法運(yùn)算結(jié)果產(chǎn)生的進(jìn)位輸出,選擇正確的加法結(jié)果輸出。進(jìn)位選擇加法器的邏輯結(jié)構(gòu)圖如圖3所示。

4 基于FPGA設(shè)計(jì)FIR數(shù)字濾波器

FIR數(shù)字濾波器的結(jié)構(gòu)如圖4所示,圖中clk1為取樣時(shí)鐘(讀數(shù)時(shí)鐘),clk2為FIR數(shù)字濾波器的工作時(shí)鐘,clk2頻率遠(yuǎn)大于clk1頻率。其工作過(guò)程:clk1時(shí)鐘的上升沿啟動(dòng)一次計(jì)算過(guò)程,控制器輸出reset信號(hào)使觸發(fā)器1清0;其后每個(gè)clk2周期計(jì)算一個(gè)h(i)[x(i)+x(N-i-1)]并進(jìn)行累加,共需N/2個(gè)clk2周期完成計(jì)算,完成計(jì)算后控制器輸出OE信號(hào)將結(jié)果輸出。

(1) 對(duì)沖激響應(yīng)系數(shù)h的處理:由Matlab設(shè)計(jì)FIR濾波器系數(shù)是一系列的浮點(diǎn)數(shù),而FPGA不支持浮點(diǎn)數(shù)的運(yùn)算,因此浮點(diǎn)數(shù)需轉(zhuǎn)換成定點(diǎn)數(shù),設(shè)計(jì)可采用Q值量化法,把系數(shù)擴(kuò)大了27=128倍,然后轉(zhuǎn)化為8位二進(jìn)制數(shù)補(bǔ)碼。較終結(jié)果再右移7位就可等到真正結(jié)果。

(2) 本設(shè)計(jì)對(duì)于有符號(hào)數(shù)采用補(bǔ)碼表示的方法,在設(shè)計(jì)中多次出現(xiàn)加法運(yùn)算,可能會(huì)產(chǎn)生溢出,所以應(yīng)進(jìn)行符號(hào)位擴(kuò)展。將符號(hào)位擴(kuò)展到輸出統(tǒng)一的較高位,才能夠保證計(jì)算結(jié)果的正確性。

擴(kuò)展方法為:

P9P8P7P6P5P4P3P2P1P0

=P9P9P9P9P9P8P7P6P5P4P3P2P1P0

其中:P9為補(bǔ)碼的符號(hào)位。

(3) Booth編碼處理由于存在求“-x”的運(yùn)算,需進(jìn)行求反加1。如果每1次調(diào)用Booth編碼都進(jìn)行加1運(yùn)算,不僅使資源大大浪費(fèi),而且由于位數(shù)較長(zhǎng),也會(huì)大大影響乘法器的速度。而本設(shè)計(jì)將加1放在Wallace樹中計(jì)算,盡管多了1級(jí)Wallace樹,但速度和資源上都大大提高了。

(4) 由于FIR是線性相位,h(i)=h(15-i),可以將乘法運(yùn)算由16次減少到8次;再通過(guò)對(duì)h(i)進(jìn)行Booth編碼可以將部分積減少到4個(gè);較終利用Wallace樹以及超快速加法器將4個(gè)部分積的相加,得到8*8乘法器的結(jié)果。由于將Booth編碼中的加1放在Wallace樹中,經(jīng)過(guò)分析需要3級(jí)Wallace樹。

5 FIR濾波器的頻率特性分析

利用Matlab中rand()和round()函數(shù)產(chǎn)生-128~128之間中100個(gè)整隨機(jī)數(shù),求幅頻響應(yīng)如圖5所示。

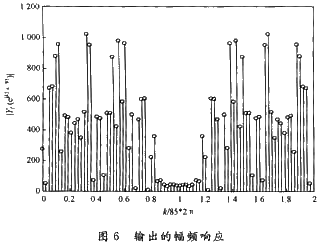

再將這100個(gè)數(shù)通過(guò)FIR濾波器,求輸出的幅頻響應(yīng)如圖6所示。

比較輸入x與輸出y的幅頻特性,可以看出FIR濾波器為低通濾波,指標(biāo)符合設(shè)計(jì)要求。

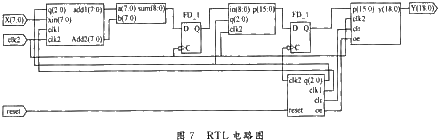

6 用ISE綜合分析FIR濾波器的性能分析

分析設(shè)計(jì)框圖可以看出,占用時(shí)間較長(zhǎng)的路徑為8位加法器——乘法器——累加器,這是影響工作頻率較主要的部分。設(shè)計(jì)中采用流水線技術(shù),在這條路徑中增加寄存器,將較長(zhǎng)路徑拆分成較短路徑,可以取得比較好的效果,提高系統(tǒng)的工作頻率。

相關(guān)閱讀:

- ...2012/03/31 10:53·基于FPGA的射頻讀卡器設(shè)計(jì)

- ...2011/12/02 16:57·基于FPGA直接序列擴(kuò)頻系統(tǒng)的設(shè)計(jì)

- ...2011/11/07 15:11·基于FPGA的高速串行傳輸系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

- ...2011/11/07 15:10·基于FPGA的通用異步收發(fā)器設(shè)計(jì)

- ...2011/11/07 15:10·基于FPGA的遠(yuǎn)距離測(cè)溫器數(shù)控系統(tǒng)設(shè)計(jì)

- ...2011/10/31 16:02·基于FPGA的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

- ...·圖文詳解汽車儀表板背后的車規(guī)級(jí)安全設(shè)計(jì)要求

- ...·使用有安全保障的閃存存儲(chǔ)構(gòu)建安全的汽車系統(tǒng)

- ...·反向偏置差分線性傳感器的較新進(jìn)展和應(yīng)用

- ...·艾德克斯測(cè)評(píng)某品牌智能插座——待機(jī)功耗篇

- ...·三線電阻式溫度檢測(cè)器測(cè)量系統(tǒng)中勵(lì)磁電流失配的影響(續(xù))

- ...·三線電阻式溫度檢測(cè)器測(cè)量系統(tǒng)中勵(lì)磁電流失配的影響

- ...·RTD測(cè)量系統(tǒng)中勵(lì)磁電流失配的影響

- ...·藍(lán)牙BR/EDR 和 Bluetooth Smart的十大重要區(qū)別

- ...·IoT網(wǎng)關(guān)平臺(tái)與應(yīng)用

- ...·增強(qiáng)版ARM DesignStart:通向定制化SoC的較快、較低風(fēng)險(xiǎn)之路

- ...·實(shí)體零售轉(zhuǎn)型O2O,倉(cāng)儲(chǔ)物流的智能化水平從何提升?

- ...·幾種車用LED驅(qū)動(dòng)方案的比較

- ...·藍(lán)牙配對(duì)第二篇:密鑰生成方法

- ...·中電瑞華推出領(lǐng)先的無(wú)線數(shù)據(jù)采集解決方案

- ...·安森美半導(dǎo)體配合市場(chǎng)趨勢(shì)的無(wú)線充電方案

- ...·安森美半導(dǎo)體配合汽車照明設(shè)計(jì)趨勢(shì)的解決方案

- ...· “芯創(chuàng)杯”首屆高校未來(lái)汽車人機(jī)交互設(shè)計(jì)大賽報(bào)名正式啟動(dòng)

- ...· 探秘第二屆衛(wèi)藍(lán)山鷹“創(chuàng)新·共享”試驗(yàn)技術(shù)論壇!

- ...· “2018中國(guó)半導(dǎo)體生態(tài)鏈大會(huì)”在江蘇省盱眙舉行

- ...· 新主題新規(guī)劃,CITE 2019瞭望智慧未來(lái)

- ...· 從汽車到工廠,TI毫米波傳感器致力于創(chuàng)造更智能的世界

- ...· 意法半導(dǎo)體(ST)、Cinemo和Valens在CES 2018展上聯(lián)合演示汽車信息娛樂(lè)解決方案

- ...· 北京集成電路產(chǎn)業(yè)創(chuàng)新發(fā)展高峰論壇即將在京召開

- ...· 三菱電機(jī)強(qiáng)勢(shì)出擊PCIM亞洲2017展

- ...· GPGPU國(guó)產(chǎn)替代:中國(guó)芯片產(chǎn)業(yè)的空白地帶

- ...· 物聯(lián)網(wǎng)產(chǎn)品設(shè)計(jì)中Wi-Fi連接的四個(gè)關(guān)鍵因素

- ...· 第三屆中國(guó)MEMS智能傳感器產(chǎn)業(yè)發(fā)展大會(huì)即將于蚌埠拉開帷幕

- ...· IAIC專項(xiàng)賽演繹“中國(guó)芯“應(yīng)用創(chuàng)新,信息安全高峰論壇亮劍海寧

- ...· 智能控制有源鉗位反激

- ...· 解讀5G毫米波OTA 測(cè)試技術(shù)

- ...· 多個(gè)市場(chǎng)高速增長(zhǎng)推動(dòng)Molex加強(qiáng)汽車領(lǐng)域的發(fā)展

- ...· 中國(guó)綠色制造聯(lián)盟成立大會(huì)召開在即 政產(chǎn)學(xué)研用共探綠色發(fā)展新模式

- ...· Efinix® 全力驅(qū)動(dòng)AI邊緣計(jì)算,成功推出Trion™ T20 FPGA樣品, 同時(shí)將產(chǎn)品擴(kuò)展到二十萬(wàn)邏輯單元的T200 FPGA

- ...· 英飛凌亮相進(jìn)博會(huì),引領(lǐng)智慧新生活

- ...· 三電產(chǎn)品開發(fā)及測(cè)試研討會(huì)北汽新能源專場(chǎng)成功舉行

- ...· Manz亞智科技跨入半導(dǎo)體領(lǐng)域 為面板級(jí)扇出型封裝提供化學(xué)濕制程、涂布及激光應(yīng)用等生產(chǎn)設(shè)備解決方案

- ...· 中電瑞華BITRODE動(dòng)力電池測(cè)試系統(tǒng)順利交付北汽新能源

- ...· 中電瑞華FTF系列電池測(cè)試系統(tǒng)中標(biāo)北京新能源汽車股份有限公司

- ...· 中電瑞華大功率高壓能源反饋式負(fù)載系統(tǒng)成功交付中電熊貓

- ...· 中電瑞華國(guó)際在電動(dòng)汽車及關(guān)鍵部件測(cè)評(píng)研討會(huì)上演繹先進(jìn)測(cè)評(píng)技術(shù)

- ...· 數(shù)據(jù)采集終端系統(tǒng)設(shè)備

- ...· 簡(jiǎn)儀科技踏上新征程

- ...· 易靈思® 宣布 AEC-Q100 資質(zhì)認(rèn)證和汽車系列產(chǎn)品計(jì)劃

- ...· 易靈思® 宣布擴(kuò)充高性能 鈦金系列™ FPGA 產(chǎn)品 鈦金系列產(chǎn)品擴(kuò)充至包含 1M 邏輯單元的 FPGA

- ...· 易靈思® 宣布Trion® Titanium 在臺(tái)積電 (TSMC) 16納米工藝節(jié)點(diǎn)流片

- ...· TI杯2019年全國(guó)大學(xué)生電子設(shè)計(jì)競(jìng)賽頒獎(jiǎng)典禮在京舉行

- ...· BlackBerry QNX虛擬機(jī)獲得全球首個(gè)汽車安全完整性等級(jí)(ASIL) ‘D’認(rèn)證

- ...· 威馬汽車選擇BlackBerry助力下一代汽車