����Microblazeܛ��FSL�������T����Ӌ�����OӋ�c���F[�D]

ժҪ���T����Ӌ���������ӹ�W����Іι���̽�y���õĔ����ɼ��O�䣬�����ռ��ι���̽�y��̽�y���Ć�������̖�����ڲ�ͬ�Ĉ�����Ҫ�õ���ͬ��Ӌ��ģʽ�����õ�Ӌ���������y�ԝM����w����������ɲɼ�Ч�ʵ��¡�ϵ�y���õ���һ�N����MicroBlazeϵ�yFSL�����ĿɔUչӋ�����OӋ�ܘ���ԓ�ܘ��܉��`������Ӳ�ͬ��Ӌ�����ܣ���ͨ�^�yһ��FSL������Microblaze CPU�cPCͨ�š���ԓ�ܘ��Ļ��A�ό��F��ᘌ����ӆ������{�،���г��õ�Ӌ��ģʽ��ϵ�y�����õ��OӋ�͌��F��ʽ�����ƏV����������Ӌ�������У��������^�͵��OӋ�����a�ɱ���

0 ����

��W�I�����������ӹ�W�I��Č�����Ҫ�M�І���ɹ��ӵ�̽�y���ڌ��F�����IJɼ���һ�㳣�õ�������һ���ι���̽�y������һ���T����Ӌ��������ǰ�˵Ćι���̽�y���Á��ռ�������̖��ÿ̽�y��һ�����Ӯa��һ��TTL�}�_����˵��T����Ӌ�����Á�ӛ�ԓTTL�����ؔ�Ŀ�����cPC����������ͨ�Ż���ͬ����APD�Ĺ�����ʽ�������Σ����T����Ӌ�����t���ھ��w�������ͬ��Ҫ��ͬ�Ĺ�����ʽ�����y��һ�Nͨ�õ�Ӌ��ģʽ�܉�M����N��r���������ڳɱ����ƣ����̶ܹ���Ӌ�����������]�ЏV韵��Ј�����Ƀr��ܸߡ���һ���棬���I�Ϳ��н�ُ�I������Ӌ���������o���M���Լ��ľ��w��������¹���Ч�ʵ��£������o���M��Ҫ��

���^�T����Ӌ��������ᘌ������������{�،���о��Ќ�������̽�y�����������Ƶġ������������{���nj����w�е�ȱ�ݣ��������c�ͽ���ʯɫ���M�п��ƣ�����̖�x��һ����ͨ�^�����l���Ć������M��̽�y���F�ġ��ڴ����г��õļ��g�����N���T����Ӌ�������rӋ�������P�����y��������������ϵ�y������һ�N�ɔUչ��ͨ�źͿ��Ƽܘ��܉����Ӳ�ͬ��ʽ��Ӌ�����ܡ�

1 ϵ�y�Y���OӋ

���wϵ�y�Y��ʾ��D��D1��ʾ��ͨ�^PC�C����̫�W�ڌ��F�cӋ��ϵ�y�Ĕ���ͨӍ�c�����ݔ��PC�C������ģʽ�x�������ͨ�^�W����ϵ�y�l�ͣ���ϵ�y���ڲ�ͬģʽ�µ�Ӌ��ֵ��Ӌ����B�Ȕ���ͨ�^�W�ڰl�͵�PC�C������PC�C�������M��̎����ϵ�y����оƬ����Xilinx��SPARTAN 3Eϵ�е�XC3S500E��ϵ�y�Ĺ���Ӌ��ݔ���Ƀɂ�BNC�ӿ����룬�@�ɂ��ӿڿ�����FPGA�M�����ã�ʹ����Ӌ�����Բ�ͬ��ģʽ�M�й�����ϵ�y�Ĺ̼�������FLASHоƬ�ȣ�SDRAM�ṩ�˴������惦���g�������\�Еr�b�dMicroblazeܛ�˴��a��Ӌ�����ô��a�Լ��惦Ӌ���Ĕ�����

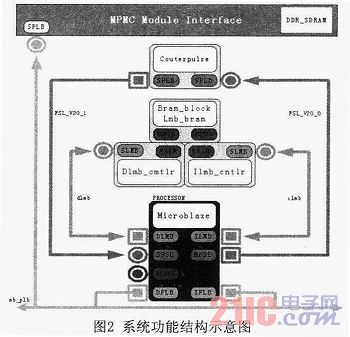

ϵ�y��FPGA��̎�����ģ����F���N����ģʽ���书�ܿ�D��D2��ʾ������ģ�K��Ҫ����ܛ��Microblaze�����ⲿ�惦���Ľӿ�MPMC���Լ���Ҫ�OӋ���F��Counterpulse IP�ˡ���Counterpulse IP���c̎����ܛ��֮�g��������FSL�����M���B�ӣ����F��Microbalze��Counterpu-lse�˵����ã��Լ���Counterpulse�˵�Microblaze�Ĕ�����ݔ��

ϵ�y�����r����Microblazeܛ��ͨ�^�W�ڽ�����PC�C�l�́�������������ͨ�^һ·FSL����������Ӌ��IP���M�й���ģʽ���x������á�Ӌ��IP�ˌ��ⲿӋ��Դ�M��Ӌ����Ӌ���ĽY���͠�B����ͨ�^��һ·FSL�����l�͵�Microblazeܛ�ˣ���Microblazeܛ�ˌ�ԓ������DDRRAM���M�о��_����ͨ�^�W�ڌ��@Щ�����^�K�l�ͽoPC�C����PC�C�M�з���̎����

ϵ�y�����N����ģʽ��ģʽһ��ʹ��Ӌ����ʹ����̖��Ч�r(���ƽ��Ч)��������Ӌ��ݔ���Ӌ���}�_��̖�M��Ӌ����ģʽ����������Ӌ���������O����Ӌ�����ڣ�������Ӌ��ݔ���Ӌ���}�_��̖�M��Ӌ����ģʽ�������Ӻ�ֹͣ��̖���_��Ӌ�r������ݔ���Ӌ��������̖��Ӌ��ֹͣ��̖(������������Ч)���M����ϵ�y���l����ʵ�Ӌ�r���Ԍ��F�����y����

2 ϵ�y�OӋ���F

2.1 ϵ�yӲ����D

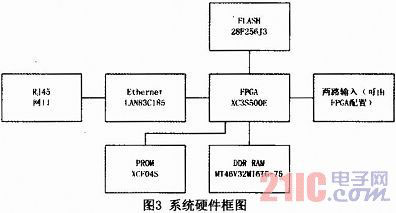

Ӌ��ϵ�yӲ���Y����D3��ʾ����FPGA��64MB��DDR�惦����16MB��FLASH�惦����10M/100M��̫�����(PHY)�ȽM�ɡ�ϵ�y�����r����PC�Cͨ�^�W�ڰl�����FPGA��FPGA�Ȳ���Microblazeܛ������Ӌ��IP�˵Ĺ���ģʽ����FPGAͨ�^��·BNC�ӿڌ��ⲿӋ��Դ�M��Ӌ��������������DDRRAM���M�о��_���^�K���@Щ����ͨ�^�W�ڰl�͵�PC�C��

2.2 ��ҪԪ������B

2.2.1 FPGAоƬ��������оƬ�x��

FPGA�x��Xilinx��˾��Spartan-3Eϵ��XC3S500E���������M��90nm���칤ˇ���a���������ܶȞ�50�f�T��Spartan3ϵ�е�FPGA��Xilinx��˾���Tᘌ����������ͳɱ����������OӋ���_�l�ģ���֧�ֶ�N�ƽ��I/O�˜ʣ������S����߉�YԴ��XC3S500E����360kbits�ĉKRAM��73kbits�ķֲ�ʽRAM��10476��߉��Ԫ��20��18×18�ij˷�����4��DCM�r犹���ģ�K��

FPGA������оƬ�x�õ���Xilinx��˾����ϵ�y�ɾ�������оƬXCF04S��ԓоƬ�ɞ�XC3S500E�ṩ����ʹ�á��ɱ����ҿ��؏;��̵����Ô������A������ԓоƬ֧��IEEE1149.1�˜ʵ�JTAG߅�����yԇ�;��̡��ڱ�ϵ�y�OӋ�У�XCF04S��Ҫ�����������Microblazeܛ�˼����ó�����������a��

2.2.2 �惦оƬ

ϵ�yʹ�õ�RAM��Micron Technology��˾��DDRSDRAM(MT46V32M16)����һƬ������512Mbit(32Mx16)��16λ�������ȴ惦оƬ��������늺���dMicroblazeܛ�˴��a�͑��ó�����a���Լ���Ӌ�������M�о��_��FLASHоƬ��Intel StrataFlash parallel NORFlash����̖��28F256J3���惦�ܶȞ�256Mbit���ڱ�ϵ�y�����ڱ���Microblazeܛ�˴��a�͑��ó�����a��

3 �����OӋ���F

3.1 ����EDK��FPGAܛ��Microblaze�đ����OӋ���F

ϵ�y�OӋ������Ҫ����Xilinx��˾��Ƕ��ʽ�_�l��EDK�����������OӋǶ��ʽ̎��ϵ�y�ļ��ɽ�Q�������������Ӳ��ƽ�_��XPS���M��ܛ�����õ�SDK��

Microblaze��Xilinx��˾�Ƴ���32λܛ̎�����ˣ�֧��CoreConnect�����Ę˜����O���ϡ�MicroBlaze̎�����\����150MHz�r��£����ṩ125 D-MIPS�����ܣ��@�N��Ч��ܛ���ڱ�ϵ�y�п����ڌ��F̎�������ܣ����F��Ӌ��IP�˵����ã��Լ�֧��Xilinx��clockgenerator��Et-hernet��IP�ˡ�ϵ�y��Ӌ�����Č��F����Verilog�Z�Ԍ�Ӌ�����ܾ�����IP�ˣ�����ͨ�^FSL��������Microblazeܛ���ϣ��Ԍ��FӋ�����ܡ�

3.2 ͨӍ�f�h

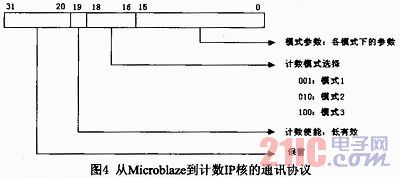

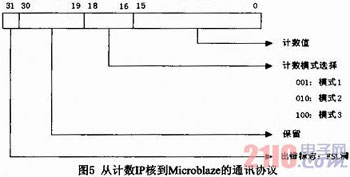

Microblaze��Ӌ��IP��֮�g��ͨӍ�������x���£�

Ӌ��IP�˵�Microblaze֮�g��ͨӍ�������x���£�

3.3 Ӌ��IP�˵��OӋ���F

3.3.1 Ӌ��IP�˵ĽY��

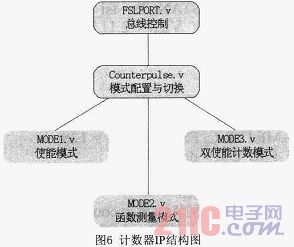

Ӌ��IP�˲���verilogӲ���Z�Ծ�������Y����D6��ʾ��플��ļ�counterpulse3���ӿ��M�����ã�������FSL�����ϵ�������x����ģʽ��pulsecount1��pulsecount2��pulsecount3�քe��3�N����ģʽ�Ĵ��a���F��fsloprt���cFSL�M�нӿڵĴ��a��

3.3.2 �cFSL�����ӿ�

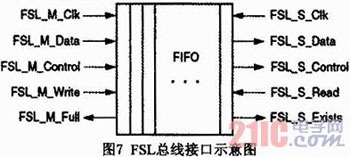

fslopn.v�Ĵ��a����cFSL�����ӿڹ��ܡ�FSL�����dž����c���c��ͨ�����������������FPGA�Ѓɂ�ģ�K�Ŀ���ͨӍ��FSL�����ǻ���FIFO�ģ����ڷǹ����ğo�ٲ�ͨ�řC�ƣ���������ǿ����O�õģ��^����Ե�8k���߂���ٵ�ͨ�����ܣ���Y����D7��ʾ��

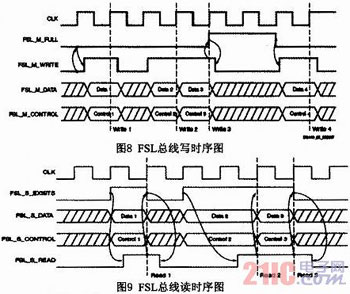

����FSL�����dž���ģ�����ϵ�y�в����˃ɗlFSL���������FMieroblaze��Ӌ��IP��֮�g���p��ͨӍ��Ӌ��IP�����挦�ɗlFSL�����r�������ķքe��MASTER(��)��SLAVE(��)�ɷN��ɫ����ˣ�fsloprt.v�Ĵ��a��ԓͬ�r�M���cFSL�����ӿڵ��x�͌��r���x���r����D8�͈D9��ʾ��

3.4 Ӌ��IP�˺�FSL��������EDK�е��B�ӌ��F

������ʹ��FSL���������ȑ�ԓ��XPS�D�ν����Ќ�Microblaze�M�����ã���Buses�Ќ�Number of FSL Links�O�Þ�1������IP Catalog�Ќ�FSL�������뵽�����ЃɴΡ�

��Ӌ��IP�˾����C��ͨ�^��ԓIP�ˌ��뵽XPS�����С�

��XPS�У��քe��Microblaze��Ӌ��IP�˵�MFSL��SFSL�M���B�ӣ���Microblaze��MFSL���B�ӵ�Ӌ��IP�˵�SFSL�ˣ���֮��Ӌ��IP�˵�MFSL���B�ӵ�Microblaze��SFSL�ˡ�����system.mhs��

���P��x:

- ...2015/01/04 10:20�����ڣ֣ͣµąf�hһ���Ԝyԇϵ�y�OӋ

- ...2014/01/26 13:16�����ڣͣӣã��У������ͣΣ���������C�ݗU��ģ�B����

- ...2012/03/23 15:58�����ڣͣã����ƣ��������ı��䉺�s�C����ϵ�y

- ...2012/03/19 11:00�����ڣͣ�����ԣãе��������Cͨ�Žӿڌ��F

- ...2011/12/07 09:33�����A���M��ӹ�˾:����MCU�����l��a���OӋ�Ŏ�ʽMP3������

- ...2011/11/30 17:25������MSP430F149�cSi4432�ğo���������W�j�Č��F����

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇