�r状��ӕr�����������

����

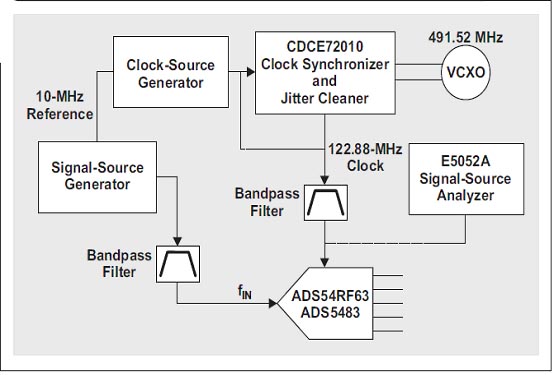

��ϵ�����¹��������֣���1 �������c��B����Μʴ_�ع���ij���r�Դ�Ķ��ӣ��������cADC �Ŀ����ӽM�ϡ��ڱ��ļ���2 �����У��@�N�M�϶��ӌ�����Ӌ��ADC �������(SNR)��֮�����c���H�y����r�M�б��^��

�V���ɘӕr犜y��

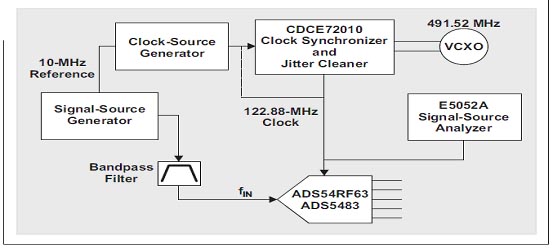

�҂�����һ��ԇĿ���Ǚz��y�Õr���λ���c��ȡ��ADC �y��SNR �ĕr状��ӵ�ƥ��̶ȡ���D11 ��ʾ��һ��ʹ��Toyocom 491.52-MHz VCXO ��TICDCE72010���ڮa��122.88-MHz �ɘӕr犣�ͬ�r�҂�����Agilent ��E5052A �팦�V����λ��ݔ���M�Мy��������һ��SNR ��Ҫ�����ڲɘӕr状��ӵ�ݔ���l�ʌ��ɷN��ͬ��TI �����D�Q����ADS54RF63 ��ADS5483���M���u�������ٸ����~׃�Q(FFT) �Ĵ�С��131000 �c��

�D11 �V����r����P�Ԝyԇ�b�ýY��

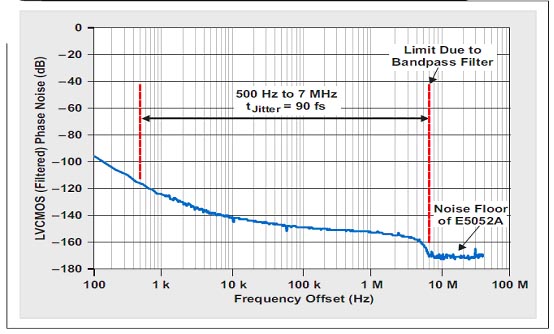

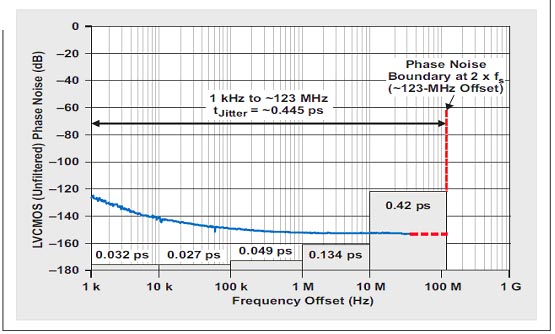

�D12 ��ʾ�����D�����˞V����CDCE72010 LVCMOS ݔ���Ĝy��ݔ����λ����131000 �c��FFT ��С���ͷe�֎����O����~500 Hz���e�������Ɏ�ͨ�V�����O������Ӱ�����λ�������D��������Ҋ�����������D��ʾ��ͨ�V�������Ƶ���λ����E5052A �������ޣ����������ڶ���Ӌ���С��V������λ��ݔ���ķe�֎���~90 fs �ĕr状��ӡ�

�D12 �V����r犵Ĝy����λ��

�������҂��������˟����������҂�ֱ�ӏ�~35 fs ���ӵĕr�Դ������ʹ�ÞV����ɘӕr犌��ɷNADC �ɘӣ���CDCE72010 ���@�^�ˡ���ݔ���l���O����10 MHz���AӋ���r状���SNR �oӰ푡�Ȼ��ͨ�^����ݔ���l����SNR ��Ҫ�鶶�����Ƶ��l�ʣ��_��ÿ��ADC �Ŀ����ӡ����ڲɘӕr状����h���ڹ�ӋADC �����ӣ����Ӌ�㑪ԓ�dz��ʴ_������߀��ע�⣬�r�Դ��ݔ������������ӣ����]�жൽ����ADC ���^���~��ֵ�����Ķ����ߕr���̖���D�Q�ʣ�ֱ��SNR �������ֹ��

�҂�֪���r�Դ�������V����ݔ�����ⲿ�r状��Ӟ�~35 fs������҂��������Üy�õ�SNR �Y����Ȼ��1 ���֣�Ո��Ҋ�����īI1���еķ���ʽ1��2 ��3 ��������ֵ���Ķ�Ӌ��õ�ADC �����ӣ�Ո��Ҋ����ķ���ʽ4����3 ���e��ÿ�NADC �y�õ�SNR �Y���Լ�Ӌ��ÿ����ӡ�

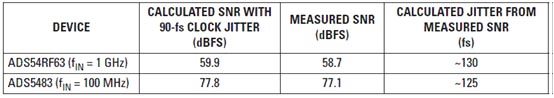

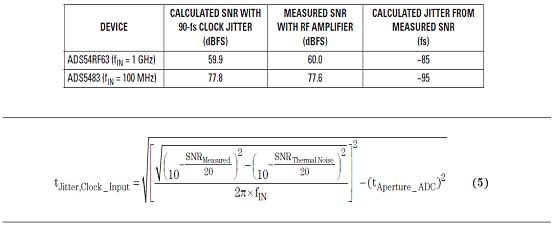

��3�y�õ�SNR ��Ӌ��ö���

����ADC �����Ӻ�CDCE72010 �IJɘӕr状��ӣ�����Ӌ���ADC ��SNR�����c���H�y���Y�����ȡ�ʹ��ADC �����ӿ���ͨ�^�y��SNR ֵӋ���CDCE72010 �IJɘӕr状��ӣ����4 ���С�էһ�����AӋSNR ֵ��Щ�ӽ��y��ֵ�����ǣ����ɷNADCӋ��ó��IJɘӕr状����c90 fs �y��ֵ���ȕr�����F��һ����ͬ�Ĉ����������ஔ��IJ�ƥ�䡣

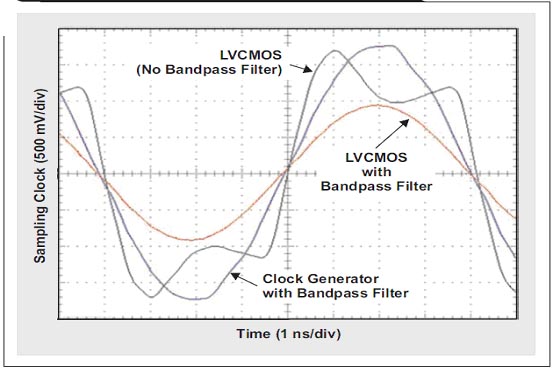

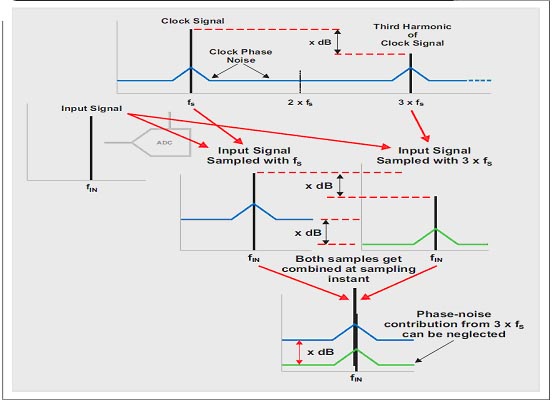

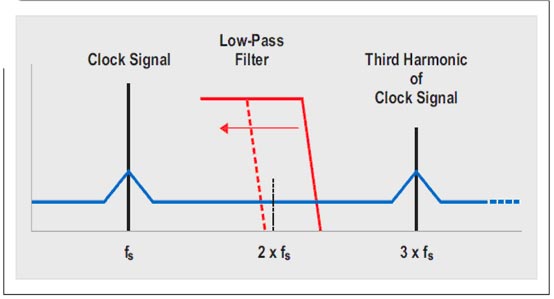

��ƥ���ԭ���ǣ�Ӌ��ó��Ŀ������ǻ��ڕr�Դ�������Ŀ����D�Q���ʡ�CDCE72010 ��LVCMOS ݔ�������˕r���̖�ĸ��A�C�������������γɿ��������ء��D13 ��ʾ���ΈD�����ˎ�ͨ�V������������δ�V��LVCMOS ݔ���D�Q���ʣ��Լ��������D�Q�����Ҳ����^�̡�

�D13 �r状��ӌ��ɘӕr��D�Q���ʵ�Ӱ�

��4 90-fs �r状��ӵ�SNR �Y��

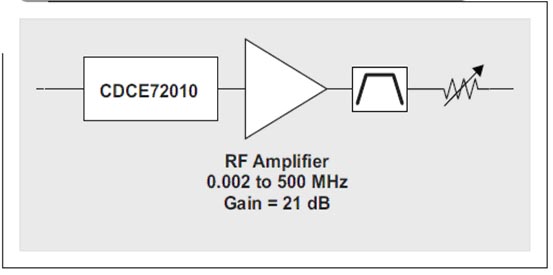

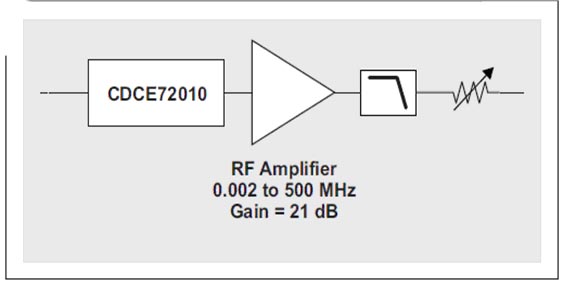

�����D�Q���ʵ�һ�N�����ǣ���CDCE72010 ��LVCMOS ݔ���͎�ͨ�V����֮�g����һ�������ஔ������ĵ���RF �Ŵ�������Ҋ�D14��ԓ�Ŵ�����ԓ�����ڞV����ǰ�棬�@�ӱ���Ԍ��䌦�r���̖����Ӱ푳̶����ڞV��������������ADC �ĕr�ݔ�뎧����������һ��ԇ�ķŴ�������21 dB �����棬����҂��ڎ�ͨ�V��������������һ����׃˥�p����ּ��ƥ��V����LVCMOS ��̖���r��������V����ݔ�����D�Q���ʡ�ԓ˥�p���ɷ�ֹADC �ĕr�ݔ�볬���^���~��ֵ��

�D14 ��ͨ�V����ǰ������RF �Ŵ����������D�Q����

ͨ�^�ڕr�ݔ��ͨ·�а��b����RF �Ŵ������ɂ������D�Q���؏��M���˸�ݔ���l�ʵ�SNR �y������Y�����5 ��ʾ���҂����Կ������y��SNR ���AӋSNR ƥ��ķdz��á�ʹ������ķ���ʽ5��Ӌ��õ��ĕr状���ֵ��90-fs �r状��ӵ�5 fs �ԃȣ���Y��ͨ�^��λ���y���ƌ��ó���

��5 90-fs �r状��Ӻ�RF �Ŵ�����SNR �Y��

δ�V���ɘӕr�ԇ�

���ˏ��{�V���ɘӕr犵���Ҫ�ԣ�����һ��ԇ��У��҂����r犎�ͨ�V������CDCE72010 ݔ����ȥ�����ڈD15 ��ʾ�Y���У��҂�ʹ����E5052A ��λ�������x�����@�r���λ�������Dz��ҵ��ǣ�ԓ�����x����λ���Ĝy���H�_����40-MHz �d���l��ƫ�ƣ��������@�c����]�нo���κ���λ�����Ե����P��Ϣ��

�D15 δ�V���ɘӕr�ݔ��Ĝyԇ�b�ýY��

Ҫ�O��ʹ��δ�V���r犕r�����_�e�����ޣ��҂������һ�Ώ���һ�²ɘ���Փ��CDCE72010 ��δ�V���r�ݔ����������һ�N���п��������صķ����������������ɕr��l�ʵĻ��l���Ҳ����A�C�������@Щ�C��������Ȼ��l�ͣ���������S�C���A���Ӷ��½���

�ڲɘӕr�g�����l���Ҳ������A�C���cݔ����̖���l����D16 ��ʾ�������˺�����Ҋ���H�@ʾ��һ���C��������ˣ����A�C���܇�����λ���cݔ����̖���l���������C��Ҳ�γ�һ�����l�Y�������ǣ����ڕr���̖�ĵ����C����������ͣ����ԓ���l�Y�������Ҳ�����͡�

�D16 �ɘӕr�g�r犻��l�����C���cݔ����̖���l

�ɂ��ɘ���̖�M����һ��r���҂����Կ�����һ����������~3 dB �r���ɵ����C������Ŀ���λ���p�����^С�����ڻ��l�͵����C��֮�g�Ľ����c��2 × fs����������λ���e����2 × fs���Եõ��ஔ�ʴ_�ĽY����

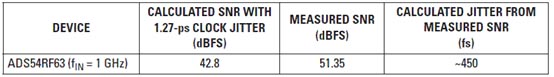

�����D19 ��ʾ��CDCE72010 ��δ�V��LVCMOS ݔ����λ����–153 dBc/Hz ������������ʼ��~10 MHz ƫ���l�ʣ�ԭ�������LVCMOS ݔ�����_���ğ�����ADS54RF63 EVM ����~1 GHz��������׃�������ĕr�ݔ�뎧���������Փ�϶��ԣ���ԓ���Ԍ���λ����e�֞�~1GHz����900-MHz ƫ���l�ʵ�3dB �r�½������@������~1.27 ps �IJɘӕr状��ӣ�����fIN = 1GHz ��SNR ����~42.8 dBFS!

�D17 ��ͨ�V����ǰ������RF�Ŵ����������D�Q����

�D18 ��ͬ��ͨ�V����������λ��

�D19 ����(extrapolate)123-MHz ƫ���l�ʵ�δ�V����λ��

���HSNR �y���Y���ȱ�6 ��

���P��x:

- ...2012/04/01 10:31���r��r状��ӷ�����һ��

- ...2012/03/19 10:04���r��r状��ӷ�����һ��

- ...2011/05/23 14:18����̖朻��A���r状��ӽ��ء��������·�r状���Ҏ�����A֪�R

- ...2009/03/11 13:16���������{ԇDDR I��II �� III�r状��ӆ��}

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇