�r��r状��ӷ�����һ��

���ߣ�Thomas Neu

���݃x�� (TI) ϵ�y�摪�ù��̎�

���͵ĸ��� ADC ���߂��ģ�Mݔ�뎧�����s���^��ɘ��l�ʵ� 3 �� 6 ����������������������S��Ƿ�ɘӑ����С�ADC �OӋ���^���Mչ�O��ؔUչ�˿���ݔ�뷶�����@��ϵ�y�OӋ�ˆT�����ȥ������һ�����g�l�ʼ����Ķ����ͳɱ����ġ���Ƿ�ɘӽ��ՙC�OӋ�б��Ҫ�eע��ɘӕr犣������һЩ��ݔ���l���r状��ӕ��ɞ���������� (SNR) ����Ҫԭ��

��ϵ�����¹��������֣����� 1 ���֡����c��B��Μʴ_�ع���ij���r�Դ�Ķ��ӣ��Լ���Ό����c ADC �Ŀ����ӽM�ϡ��ڡ��� 2 ���֡��У�ԓ�M�϶��ӌ�����Ӌ�� ADC �� SRN��Ȼ�����c���H�y���Y�����ȡ����� 3 ���֡�����B���ͨ�^���� ADC �Ŀ����Ӂ��Mһ������ ADC �� SNR���������c��B�r���̖�D�Q���ʵă�����

�ɘ��^�����

���� Nyquist-Shannon �ɘӶ�������������كɱ������^���l�ʵ����ʁ팦ԭʼݔ����̖�ɘӣ��t����Եõ���ȫ�ؽ������O�� 100 MSPS �����ʌ����_ 10MHz ��ݔ����̖�ɘӣ��t����ԓ��̖��λ�� 1 �� 10MHz �Ļ������ׂ�Nyquist �^��߀���� 100 �� 110MHz �ĸ��� Nyquist �^���Ƿ�ɘӣ����]�Pϵ��Ո��Ҋ�D 1�����ڸ��ߣ��ڶ������������ȣ�Nyquist �^���вɘӣ�һ�㱻�Q��Ƿ�ɘӻ�βɘӡ�Ȼ������ ADC ǰ��Ҫ��ʹ�ÿ���B�^�V���Ԍ����� Nyquist �^��ɘӣ�ͬ�r�����ؽ�ԭʼ��̖�^���Юa���ɔ_��

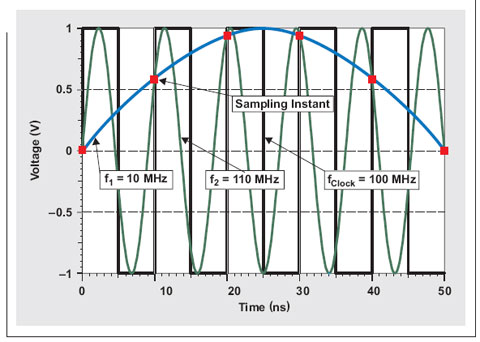

�D 1 100MSPS �ɘӵăɂ�ݔ����̖�@ʾ�˻�B��������ͬ�ɘ��c

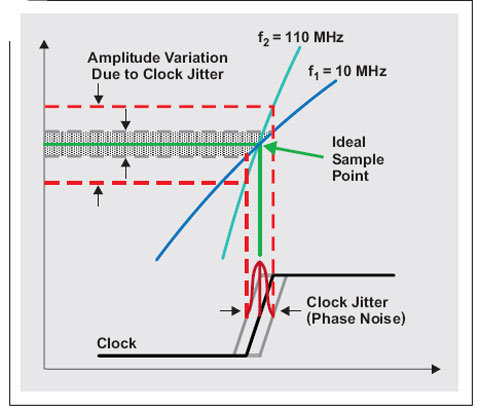

�м��^��ij���ɘ��c�����Կ���Ӌ�r���ʣ��r状��ӻ�r���λ����������γ����׃���ġ����ڸ� Nyquist �^�����磬f1 = 10 MHz �� f2 = 110 MHz��Ƿ�ɘӎ���ݔ���l�ʵ����ӣ��̶������ĕr状���������ɘ��c�a�������������ƫ����������⣬�D 2 �����r���̖�����D�Q���ʌ��ɘӕr�g��׃���a����Ӱ푡��D�Q���ʛQ���˕r���̖ͨ�^�㽻���c�Ŀ������Q��Ԓ�f���D�Q����ֱ��Ӱ� ADC �Еr��·���|�l�ֵ��

�D 2 �r状����γɸ������ݔ����̖����`��

�r状��ӌ��µ� SNR �p��

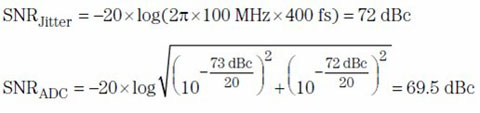

�Ўׂ����ؕ����� ADC �� SNR�����磺���������ܾ�ʽ�D�Q����һ�㲻���@�������������ڵ�ݔ���l�������� SNR�����Լ��r状��ӣ�SNRJitter����Ո��Ҋ���淽��ʽ 1����SNRJitter �����ܵ�ݔ���l�� fIN��ȡ�Q�� Nyquist �^�����ƣ�ͬ�r�ܿ��r状����� tJitter �����ƣ���Ӌ�㷽�����£�

SNRJitter[dBc]=-20��log(2����fIN��tJitter)(2)

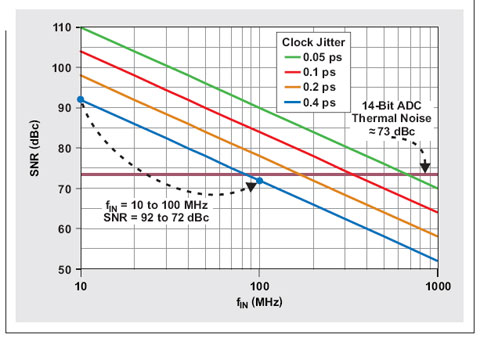

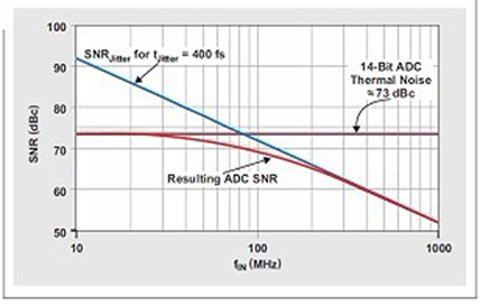

�����҂��AӋ���ǘӣ����ù̶������ĕr状��ӣ�SNR �Sݔ���l���������½����D 4 �������@�N�F�����@ʾ�� 400 fs �̶��r状��ӕrһ�� 14 λ�ܾ�ʽ�D�Q���� SNR�����ݔ���l������ʮ�������磺�� 10MHz ���ӵ� 100MHz���t�r状��ӎ������^���H SNR ���� 20dB��

��ǰ���������� ADC SNR ����һ����Ҫ������ ADC �ğ������䲻�Sݔ���l��׃����һ�� 14 λ�ܾ�ʽ�D�Q��һ���� ~70 �� 74 dB �ğ�������D 4 ��ʾ���҂������ڮaƷ�f�������ҵ� ADC �ğ��������ஔ���^��ָ��ݔ���l�ʣ������О� 10MHz���� SNR�����Еr状���߀����һ�����ء�

�҂��팦һ������ 400 fs ���ӕr��·�� ~73 dB ������ 14 λ ADC �M�з�������ݔ���l�ʣ����磺10MHz �ȣ��£�ԓ ADC �� SNR ��Ҫ����������x������ݔ���l��������400-fs �r状���Խ��Խռ��������ֱ�� ~300 MHz �r��ȫ�ӹܡ��M����� 10MHz �� SNR��100MHz ݔ���l���r状��ӎ����� SNR ÿʮ���l���� 20dB�����ǿ� SNR �H���� ~3.5 dB������ 69.5dB���������� 73-dB ������Ո��Ҋ�D 5����

�F�ڣ������@����� ADC �ğ������ӣ�����ݔ���l�ʲɘӕr�r状��ӱ�dz���Ҫ�����磬һ�� 16 λ ADC ���� ~77 �� 80 dB �ğ����ӡ������D 4 ��ʾ�����D�������^С�� 100MHz ݔ���l�� SNR �ĕr状���Ӱ푣��r状�������s 150 fs ����ߡ�

�_���ɘӕr状���

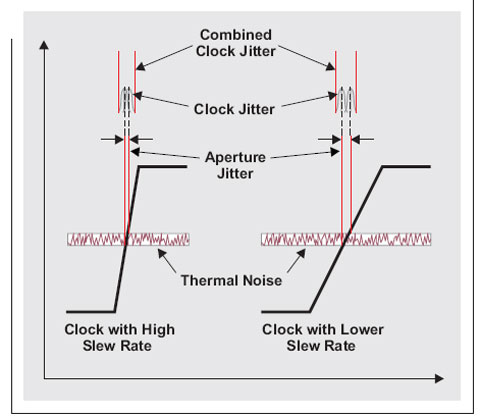

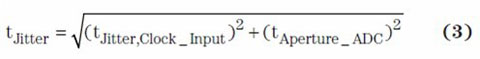

��ǰ�������ɘӕr状����ɕr犵�Ӌ�r���ʣ���λ������ ADC �Ĵ��ڶ��ӽM�ɡ��@�ɂ����ֽY�ϽM�����£�

�҂��ڮaƷ�f�����п����ҵ� ADC �Ŀ��ڶ��� (aperture jitter)���@һֵһ���c�r�������D�Q����һ��ָ����ӛס�@һ�c����Ҫ���͕r�����������D�Q���ʣ��Ķ����Ӵ��ڶ��ӡ�

�r�ݔ�붶��

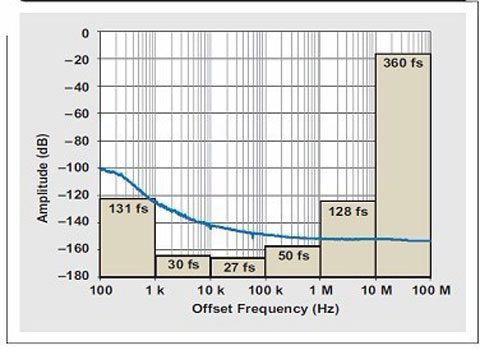

�r�朣���ʎ�����r犾��_���� PLL����������ݔ������һ��Ҏ����ij���l�ʷ����ȣ�ԓ�l��ͨ��ƫ�x�ڻ����r��l�� 10 kHz �� 20 MHz����λҲ������������L�Ƴ���λ���D�������Ԍ������ϵ�һ��@ȡ������Ϣ�����ǣ��Ͷ˵� 10kHz �߶˵� 20MHz �Еr�������_��ʹ��߅�磬��������{ԇ��ه������ϵ�y�������҂����ں����M��Ԕ����B���D 6 �������O�����_�������Ƶ���Ҫ�ԣ��D�е���λ���D����ÿʮ���l���Ӄ��ݸ��w���҂����Կ���������������O���� 100-Hz �� 10kHz ƫ�ƣ��t�a���Ķ��ӱ�O�鲻ͬ��ͬ�ӵأ����磬�O�����������ƞ� 10 �� 20MHz���ɵõ���� 100MHz �O�ØO�鲻ͬ�ĽY����

�D 5 �a���� ADC SNR �ܟ����͕r状��ӵ�����

�D 6 ÿʮ���lӋ��õ��ĕr���λ������Ӱ�

���P��x:

- ...2012/04/01 10:31���r��r状��ӷ�����һ��

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇