����Virtex-5 FPGA�ĸ��ٴ��Ђ�ݔϵ�y(t��ng)���O(sh��)Ӌ(j��)�c��(sh��)�F(xi��n)[�D]

Ŀǰ�����ٴ��нӿ�ȡ��������?f��)�Y(ji��)��(g��u)�ѽ�(j��ng)�Ǵ����څ����(d��ng)��ܶ�û��B��(bi��o)��(zh��n)(��USB��PCI-Express)���ǻ��ڴ����B�Ӂ팍(sh��)�F(xi��n)���ق�ݔ?sh��)ġ�����ڲ��п����������B�ӵ������o�ܶȺ��·�g�Ծ��кܶ���(y��u)�ݡ���ˣ��ܶ���ݔ�I(l��ng)���D(zhu��n)���˴��Ђ�ݔ����Pӛ����X�@ʾ���B�����ٱ��廥�B�ʹ惦����(n��i)�����B��ԓϵ�y(t��ng)�漰���ļ��g(sh��)��Ҫ���������w��ݔ��PCIE(PCI-Express)��ݔ��DDR���漼�g(sh��)���Լ��@�N���g(sh��)��FPGA���ںϞ�һ��(g��)�����Ĵ��Ђ�ݔ�·������(sh��)�F(xi��n)���ڃ��_����(w��)��֮�g�ĸ��ٔ�(sh��)��(j��)��ݔ�yԇ���@���ڌ�(sh��)�H���̑�(y��ng)�þ�����Ҫ�ĬF(xi��n)��(sh��)���x��

1 ϵ�y(t��ng)�Y(ji��)��(g��u)

����

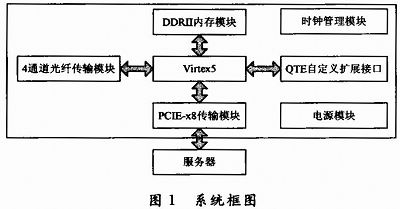

���ٴ��Ђ�ݔϵ�y(t��ng)���锵(sh��)��(j��)�ɼ�����ݔ���惦�е�һ���֣�����ݔ����ָ��(bi��o)������(y��n)���Ҫ��ԓϵ�y(t��ng)Ҫ��ɹ���̖��PCI-Express�ӿ���̖����D(zhu��n)�Q�������D(zhu��n)�Q�^������ɔ�(sh��)��(j��)�ĸ��ق�ݔ����̖һ����_(d��)4.25Gb/s��̎����˸ߵĔ�(sh��)��(j��)��Ӳ���O(sh��)Ӌ(j��)����˺ܴ������(zh��n)��������������Ӳ���У����ٹ���D(zhu��n)�Q�·��F(xi��n)PGA��(sh��)��(j��)̎���·��DDR��(sh��)��(j��)�����·���r(sh��)犹����·��PCIE��ݔģ�K�·���Դģ�K�·���Զ��x�U(ku��)չ�ӿ��·��ϵ�y(t��ng)��D��D1��ʾ��

���g(sh��)Ҫ����Ҫ�������c(di��n)�����ȣ���ݔ���е�4��(g��)���wͨ����ÿͨ��Ҫ�_(d��)��2Gb/s���ϡ���Σ�PCIE��ݔ���ʲ�С��6Gb/s��֧��DMA��ݔ�����У����w��PCI-E��ݔ�`�a��ҪС��1×10-10���B�m(x��)��ݔ������(w��n)����

�D1�и���(g��)ģ�K�Ĺ������£�Virtex5�����ݔ���ĺ��ģ��Á팍(sh��)�F(xi��n)��(sh��)��(j��)�Ĺ��w�ӿڵ�PCIE�ӿڵĸ����D(zhu��n)�Q�����w��ݔģ�K�������nj���(n��i)����(sh��)��(j��)��(j��ng)�^���a��ͨ�^���|��ݔ�o����ϵ�y(t��ng)���Լ���������┵(sh��)��(j��)�������┵(sh��)��(j��)���ͽoFPGA̎���·DDR����ģ�K�����ã����nj���ݔ�^���еĸ��ٔ�(sh��)��(j��)���M(j��n)�о��棬�Ա���?j��n)?sh��)��(j��)�������ԡ�PCI-Express��ݔģ�K�����ã������cPC֮�g��(sh��)�F(xi��n)PCI-Express��ݔ�f(xi��)�h���cPC��(sh��)�F(xi��n)���Д�(sh��)��(j��)��ݔ��ͬ�r(sh��)�c�ⲿ�U(ku��)չ�ӿڣ�DDR���棬���w��ݔģ�K��(sh��)�F(xi��n)��(n��i)�����Д�(sh��)��(j��)�Ľ��Q��QTE�Զ��x�ӿ�ģ�K�����ã������M(j��n)���ⲿ���ܔU(ku��)չ�����磬���ԔU(ku��)չ���ٔ�(sh��)��(j��)�ɼ��忨���惦Ӳ�P�����D��ɼ����ȡ��r(sh��)犹���ģ�K�����ã��ǽo���w��ݔģ�K�ṩ�����r(sh��)犡��r(sh��)��l����FPGA�ĕr(sh��)犿���ģ�K���ơ�����(j��)��ģ�K�����ܣ��o��ָ���ĕr(sh��)犡�PCI-Express�ą����r(sh��)犣���ͨ�^оƬ��PC��������ȡ�ġ��Դ����ģ�K�����ã��ǽo����(g��)ϵ�y(t��ng)�ṩ���N��ͬ��늉���

2 ϵ�y(t��ng)ģ�K�O(sh��)Ӌ(j��)�c��(sh��)�F(xi��n)

���ˌ�(sh��)�F(xi��n)��Ҫ���ϵ�y(t��ng)���ã����õذl(f��)�]��ģ�K�������֮�g�����ã���회�ģ�K�g�M(j��n)��ϵ�y(t��ng)�ąf(xi��)�h������ԓϵ�y(t��ng)�Ĕ�(sh��)��(j��)��ݔ���p��ģ��ȿ��Ԃ�ݔ��(sh��)��(j��)��Ҳ���Խ��Ք�(sh��)��(j��)������Ҫ���Դ����ģ�K���r(sh��)犹���ģ�K��PCI-Express��ݔģ�K��DDR����ģ�K�����w��ݔģ�K���ⲿ�U(ku��)չ�ӿڽM�ɡ����У��r(sh��)犿���ģ�K��Aurora�l(f��)��ģ�K��Aurora����ģ�K������(g��)�O(sh��)Ӌ(j��)�����c(di��n)��

2.1 �r(sh��)犿���ģ�K

�r(sh��)犿���ģ�K��Ҫ�Á�����FPGA����ĕr(sh��)�оƬICS8442���a(ch��n)������Ҫ�ĸ�����ȡ��Ͷ��ӵIJ�֕r(sh��)犡�

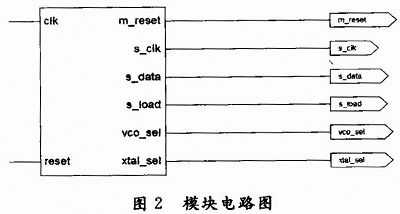

��ģ�K�·��D2��ʾ��ݔ�����е���̖�Á���Ɍ�ICS8442�ľ��̣�ʹ���܉�a(ch��n)������Ҫ�ĕr(sh��)���̖��

ICS8442�����܅���(sh��)���£�

ݔ����̖�l�ʷ�����31.25��700MHz�������l�ʷ�����10��25MHz��VCO�l�ʷ�����250��700MHz��ICS8442��LVDS߉�ƽ�����ИO�͵���λ�����@�N����ʹ���dz��m���Á�鼪������̫�W(w��ng)��ͬ�����w�W(w��ng)�ṩ�r(sh��)���̖��

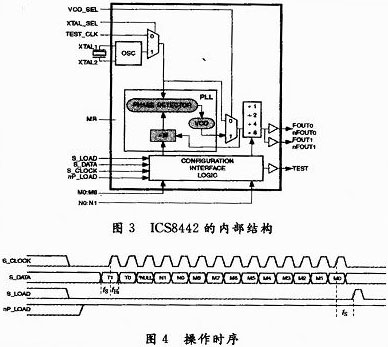

ICS8442�ă�(n��i)���Y(ji��)��(g��u)�D3��ʾ��ICS8442��(n��i)����һ��(g��)������PLL�i��h(hu��n)����VCO��ݔ���l�ʷ�����250��700MHz֮�g�����lϵ��(sh��)����M�Q���ģ�M��ȡֵ������10��28֮�g��VCO��ݔ���l�ʞ飺

![]()

ICS8442�^�K��ݔ���Y(ji��)��߀Ҫ��(j��ng)�^һ��(g��)���l��N���^�Kݔ���Y(ji��)�����l�ʺ;���ݔ���l�ʵ��P(gu��n)ϵʽ�飺

![]()

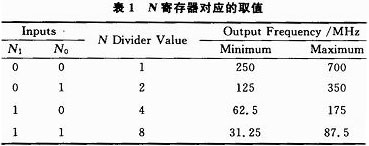

�У�N��һ��(g��)2λ�ļĴ������䌦��(y��ng)��ȡֵ���1��ʾ��

��ICS8442�r(sh��)�оƬ�IJ�����Ҫ�nj��Ĵ���M��N�Č�������ICS8442֧�ֲ��Ќ������ʹ��Ќ�����������(j��)Ӳ���·���O(sh��)Ӌ(j��)��������ô��еČ������r(sh��)��(d��ng)ICS8442��nP_LOAD�Þ���ƽ��S_LOAD�Þ���ƽ�r(sh��)��оƬ��(sh��)�F(xi��n)���в����������r(sh��)����D4��ʾ��

��(d��ng)S_LOAD�Þ����nP_LOAD�Þ��֮��(sh��)��(j��)��S_CLOCK��������̎�Ĵ��ھ��_���У���S_LOAD���½���̎����(sh��)��(j��)�i�浽�Ĵ���M��N�С�

����AURORA���wͨ�ŵ�ݔ���r(sh��)��l���O(sh��)������125MHz���Y(ji��)��Ӳ���·���O(sh��)Ӌ(j��)��Ӳ��������l�ʞ�20MHz������x��Mֵ��000011001(25)��N��ֵ��10(4)���ʕr(sh��)�оƬ�ĕr(sh��)�ݔ���l�ʞ飺

![]()

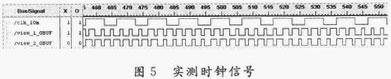

�r(sh��)犿���ģ�K�Č�(sh��)�y�r(sh��)���̖��D5��ʾ��

�D5����Chipscope�ھ�߉�����x�õ��IJ��Σ�����Chipscope�ھ�߉�����x���|�l(f��)�r(sh��)���100MHz�������ץȡ125MHz�ĕr(sh��)���̖�r(sh��)���ڈD���@ʾ�ĕr(sh��)���̖ռ�ձȲ������r(sh��)�оƬ�a(ch��n)���ĕr(sh��)��l�ʽ��ͣ��t�ˬF(xi��n)����ʧ��

2.2 AURORA�l(f��)��ģ�K

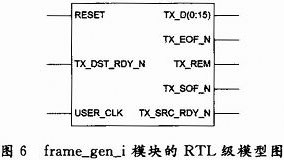

������AURORA IP CORE�r(sh��)��ͬ�r(sh��)������һ��(g��)����AURORA�f(xi��)�h����ʾ������ˣ�Ҫ��(sh��)�F(xi��n)����AURORA�f(xi��)�h�Ĺ��wͨ�ţ��ڰl(f��)�Ͷ�ֻ��Ҫ��frame_gen_iģ�K��Ҫ�l(f��)�͵Ĕ�(sh��)��(j��)�����Ȼ��ͨ�^AURORAģ�K�l(f��)�ͳ�ȥ�����ԓģ�K���ؽ�B��Ό���һ�������^���Ĕ�(sh��)��(j��)�M(j��n)�д�����s���γ��m��AURORA�f(xi��)�h�Ĕ�(sh��)��(j��)����ͨ�^AURORA�f(xi��)�h�l(f��)�͵����նˡ��D6��frame_gen_iģ�K��RTL��ģ�͈D��

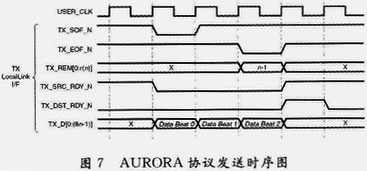

���]����һ����ݔ��(sh��)��(j��)���ʿ��ܕ��cAURORA��ݔ?sh��)ĕr(sh��)��l�ʲ�ͬ������ڰl(f��)�Ͷ˽���һ��(g��)FIFO�������_��������AURORA�f(xi��)�h�İl(f��)�͕r(sh��)��D��D7��ʾ�����Կ�����TX_SOF_N�锵(sh��)��(j��)�������_ʼ��(bi��o)־��TX_EOF_N�锵(sh��)��(j��)�����ĽY(ji��)��.��(bi��o)־��TX_REM[0��r(n)]ӛ��^��Ă�ݔ��(sh��)��(j��)�ľ��̣�TX_SRC_RDY_N��ʹ��픵(sh��)��(j��)��Ч��TX_DST_RDY_N��ʹ����(zh��n)��ý��ܔ�(sh��)��(j��)��TX_D[0��(8n-1)]�Ǵ�ģ�K��ݔ����(sh��)��(j��)��������Ϣ��AURORA�f(xi��)�h�İl(f��)�͕r(sh��)����ʹ��FIFO�����_�r(sh��)Ҳ��(y��ng)ԓ��ѭ�@�ӵąf(xi��)�h��

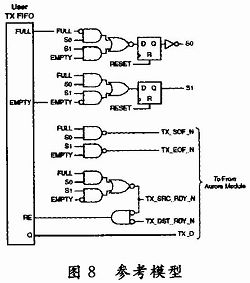

�l(f��)�Ͷ˵�FIFOģ�K�քe����FIFO�ď�(f��)λ��̖��FIFO�ա�FIFO�M���Լ��x/���r(sh��)犡�ʹ�͔ܺ�(sh��)��(j��)��̖������ˑ�(y��ng)ԓ����(j��)FIFO�Ę�(bi��o)־λempty��full���a(ch��n)��AURORA�İl(f��)�͕r(sh��)����ģ����D8��ʾ����(d��ng)RESET��̖����֮�r(sh��)�����Ȍ�S0�Þ���ƽ����S1�Þ���ƽ��ͬ�r(sh��)����(j��)FULL��EM-PTY�Ġ�B(t��i)�_��������S0��S1�Ġ�B(t��i)���M(j��n)������(j��)����߉�P(gu��n)ϵ�õ�TX_SOF_N��TX_EOF_N��TX_SRC_RDY_N��߉��̖�����Ҹ���(j��)��(sh��)��(j��)X_DST_RDY_N��TX_SRC_RDY_N����FIFO���xʹ�ܡ�������߉���Կ�����ֻ����FULL��1��EMPTY��0�r(sh��)��F(xi��n)IFO���xʹ�ܲ��ܱ����_��TX_SOF_N�锵(sh��)��(j��)���Ď��^��(bi��o)־��TX_EOF_N�锵(sh��)��(j��)���Ď�β��(bi��o)־��TX_STC_RDY_N��͕r(sh��)���픵(sh��)��(j��)��Ч��TX_DST_RDY_N��ݔ����̖������(j��)��ݔ����̖�_��FIFO���x���r(sh��)��

��FIFO�r(sh��)�������Ҫ����(j��)�����·�D���a(ch��n)�����������·�D�У���һ��(g��)D�|�l(f��)������RESET��̖�Ǐ�(f��)λ��̖����(f��)λ���nj��|�l(f��)��ݔ���˿����㣬����S0��1����S1��0����֮ǰ�ij������`���@�������RESET��̖����֮��S0��0��S1��1���@�ӌ�(d��o)�µĽY(ji��)�������^�_ʼݔ���һ�Δ�(sh��)��(j��)�Gʧ��֮��ĽY(ji��)��ݔ����������(j��ng)�^�������֮��z������}���Ѹ�����

2.3 AURORA����ģ�K

ͬ����AURORA�f(xi��)�hģ�K�У�Ҫ��(sh��)�F(xi��n)����(sh��)��(j��)�Ľ��գ�ֻ����frame_checkģ�K�Ќ����յĴ��a�����ģ������Լ�����Ҫ�ă�(n��i)�ݣ���Ɍ���(sh��)��(j��)�Ľ�a��ȡ����������Ϣ������ɔ�(sh��)��(j��)�ľ��档

���P(gu��n)��x:

- ...2012/06/13 11:24������VPN�cOPC����ˮ̎��S�h(yu��n)�̱O(ji��n)��ϵ�y(t��ng)

- ...2012/04/09 16:22�����ڣ֣õ����ⲻ���ཻ��߅���²ü��㷨

- ...2011/11/28 14:39������VerilogHDL�V�������O(sh��)Ӌ(j��)

- ...2011/10/21 15:42������VB�Z�ԵęC(j��)������������ِ�c�����о�

- ...2011/10/08 13:45������Verilog HDL��CMOS�D���������(q��)���·

- ...2009/12/18 15:31������VC++�ĵ͉�����ɿ��ԙz�yϵ�y(t��ng)

- ...���D��Ԕ����܇�x���屳���܇Ҏ(gu��)����ȫ�O(sh��)Ӌ(j��)Ҫ��

- ...��ʹ���а�ȫ���ϵ��W��惦��(g��u)����ȫ����܇ϵ�y(t��ng)

- ...������ƫ�ò�־��Ԃ��������^���M(j��n)չ�͑�(y��ng)��

- ...�����¿�˹�y�uijƷ�����ܲ����������C(j��)����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�(�m(x��))

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...���{(l��n)��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^(q��)�e

- ...��IoT�W(w��ng)�P(gu��n)ƽ�_�c��(y��ng)��

- ...������(qi��ng)��ARM DesignStart��ͨ���ƻ�SoC���^�졢�^���L(f��ng)�U(xi��n)֮·

- ...����(sh��)�w�����D(zhu��n)��O2O���}�����������ܻ�ˮƽ�ĺ�������

- ...���N܇��LED�(q��)�ӷ����ı��^

- ...���{(l��n)���䌦�ڶ�ƪ��������ɷ���

- ...��������A�Ƴ��I(l��ng)�ȵğo����(sh��)��(j��)�ɼ���Q����

- ...����ɭ���댧(d��o)�w����Ј�څ�ݵğo����늷���

- ...����ɭ���댧(d��o)�w�����܇�����O(sh��)Ӌ(j��)څ�ݵĽ�Q����

- ...�� ��о��(chu��ng)�����ø�Уδ����܇�˙C(j��)�����O(sh��)Ӌ(j��)��ِ��(b��o)����ʽ����

- ...�� ̽�صڶ����l(w��i)�{(l��n)ɽ������(chu��ng)�¡�������ԇ�(y��n)���g(sh��)Փ����

- ...�� ��2018�Ї��댧(d��o)�w���B(t��i)朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ(gu��)����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�(chu��ng)������ܵ�����

- ...�� �ⷨ�댧(d��o)�w��ST����Cinemo��Valens��CES 2018չ��(li��n)����ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a(ch��n)�I(y��)��(chu��ng)�°l(f��)չ�߷�Փ�������ھ����_

- ...�� ����늙C(j��)��(qi��ng)�ݳ���PCIM����2017չ

- ...�� GPGPU���a(ch��n)������Ї�оƬ�a(ch��n)�I(y��)�Ŀհ؎�

- ...�� ��(li��n)�W(w��ng)�a(ch��n)Ʒ�O(sh��)Ӌ(j��)��Wi-Fi�B�ӵ��Ă�(g��)�P(gu��n)�I����

- ...�� �������Ї�MEMS���܂������a(ch��n)�I(y��)�l(f��)չ��������ڰ������_�Ļ

- ...�� IAIC���(xi��ng)ِ���[���Ї�о����(y��ng)�Ä�(chu��ng)�£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g(sh��)

- ...�� ����(g��)�Ј��������L�Ƅ�Molex�ӏ�(qi��ng)��܇�I(l��ng)��İl(f��)չ

- ...�� �Ї��Gɫ����(li��n)�˳���������_�ڼ� ���a(ch��n)�W(xu��)���ù�̽�Gɫ�l(f��)չ��ģʽ

- ...�� Efinix® ȫ���(q��)��AI߅��Ӌ(j��)�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r(sh��)���a(ch��n)Ʒ�U(ku��)չ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M(j��n)���������I(l��ng)�ǻ�������

- ...�� ��늮a(ch��n)Ʒ�_�l(f��)���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧(d��o)�w�I(l��ng)�� ����弉�ȳ��ͷ��b�ṩ���W(xu��)���Ƴ̡�Ϳ�������⑪(y��ng)�õ����a(ch��n)�O(sh��)���Q����

- ...�� ������ABITRODE����늳yԇϵ�y(t��ng)���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y(t��ng)�И�(bi��o)��������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ(f��)�dϵ�y(t��ng)�ɹ����������؈

- ...�� ������A���H��늄���܇���P(gu��n)�I�����y�u��ӑ�������[���M(j��n)�y�u���g(sh��)

- ...�� ��(sh��)��(j��)�ɼ��K��ϵ�y(t��ng)�O(sh��)��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|(zh��)�J(r��n)�C����܇ϵ�Юa(ch��n)ƷӋ(j��)��

- ...�� ���`˼® �����U(ku��)������� ⁽�ϵ��™ FPGA �a(ch��n)Ʒ ⁽�ϵ�Юa(ch��n)Ʒ�U(ku��)�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ��(ji��)�c(di��n)��Ƭ

- ...�� TI��2019��ȫ����W(xu��)������O(sh��)Ӌ(j��)��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C(j��)�@��ȫ���ׂ�(g��)��܇��ȫ�����Եȼ�(ASIL) ��D���J(r��n)�C

- ...�� ���R��܇�x��BlackBerry������һ����܇