����VerilogHDL�V�������O(sh��)Ӌ(j��)

�F(xi��n)��Ӌ(j��)��C(j��)��ͨ��ϵ�y(t��ng)�ЏV�����Ô�(sh��)����̖(h��o)̎���ļ��g(sh��)�ͷ����������˼·���Ȱ���̖(h��o)��һϵ�еĔ�(sh��)�ց���ʾ��Ȼ��(du��)�@Щ��(sh��)����̖(h��o)�M(j��n)�и��N���ٵĔ�(sh��)�W(xu��)�\(y��n)�㡣��Ŀ���Ƕ�N���ӵģ��е��Ǟ��˼��ܣ��е��Ǟ���ȥ�����ȟo�P(gu��n)����Ϣ���Q��V�����Еr(sh��)Ҳ��ijЩ�NĔ�(sh��)����̖(h��o)̎���\(y��n)��ɞ�׃�Q�����xɢ�ĸ����~׃�Q��С��׃�Q�ȡ�VerilogHDL��Ŀǰ��(y��ng)���^�V����һ�NӲ�������Z�ԣ����ڔ�(sh��)�����ϵ�y(t��ng)���O(sh��)Ӌ(j��)���������M(j��n)�и��N��(j��)�e��߉�O(sh��)Ӌ(j��)�����M(j��n)�Д�(sh��)��߉ϵ�y(t��ng)�ķ����(y��n)�C���r(sh��)�������߉�C�ϡ�С���V�������O(sh��)Ӌ(j��)���ڏ�(f��)�s�㷨���·�O(sh��)Ӌ(j��)���������Veril—ogHDL��(du��)�p����С���V�����M(j��n)�н�ģ�����棬��(sh��)�F(xi��n)�·���Ԅ�(d��ng)���O(sh��)Ӌ(j��)������һ�N�^������ķ�����

Verilog HDL��B

Verilog HDL��һ�NӲ�������Z�ԣ���һ�N���ı���ʽ��������(sh��)��ϵ�y(t��ng)Ӳ���ĽY(ji��)��(g��u)���О���Z�ԣ��������Ա�ʾ߉�·�D��߉���_(d��)ʽ��߀���Ա�ʾ��(sh��)��߉ϵ�y(t��ng)����ɵ�߉���ܡ� Verilog HDL��VHDL��Ŀǰ�������^���еăɷNӲ�������Z�ԣ�������20���o(j��)80��������_�l(f��)�����ġ�ǰ����Gateway Design Automation��˾�_�l(f��)���ɷNHDL����IEEE��(bi��o)��(zh��n)��

Verilog HDL��������;�^�V����C�Z�ԵĻ��A(ch��)�ϰl(f��)չ������һ�NӲ�������Z�ԣ�������GDA��˾��PhilMoorby��1983��ĩ�ׄ�(chu��ng)�ģ��^��ֻ�O(sh��)Ӌ(j��)��һ��(g��)�����c�(y��n)�C���ߣ�֮������m(x��)�_�l(f��)�����P(gu��n)�Ĺ���ģ�M�c�r(sh��)��������ߡ�1985��Moorby�Ƴ����ĵ�����(g��)���÷�����Verilog-XL,�@���˾�ijɹ����Ķ�ʹ��Verilog HDLѸ�ٵõ��ƏV��(y��ng)�á�1989��CADENCE��˾��ُ(g��u)��GDA��˾��ʹ��VerilogHDL�ɞ���ԓ��˾�Ī�(d��)�Ҍ�����1990��CADENCE��˾���_�l(f��)����Verilog HDL,������LVI�M���Դ��M(j��n)Verilog HDL�ɞ�IEEE��(bi��o)��(zh��n)����IEEE Standard 1364-1995.

Verilog HDL���^�����c(di��n)�����W(xu��)���ã������C�Z�Եľ��̽�(j��ng)�(y��n)��������һ��(g��)�^�̵ĕr(sh��)�g��(n��i)�ܿ�ČW(xu��)��(x��)�����գ��������Verilog HDL��(n��i)�ݰ������cASIC�O(sh��)Ӌ(j��)�����P(gu��n)�n�̃�(n��i)���M(j��n)���v�ڣ�����HDL�Z�Ա����nj��T����Ӳ���cϵ�y(t��ng)�O(sh��)Ӌ(j��)�ģ��@�ӵİ��ſ���ʹ�W(xu��)��(x��)��ͬ�r(sh��)�@���O(sh��)Ӌ(j��)��(sh��)�H�·�Ľ�(j��ng)�(y��n)���c֮��ȣ�VHDL�ČW(xu��)��(x��)Ҫ���yһЩ����Verilog HDL�^���ɵ��Z����Ҳ������ɳ��W(xu��)�߷�һЩ�e(cu��)�`���@һ�c(di��n)Ҫע�⡣

l С���V�������O(sh��)Ӌ(j��)

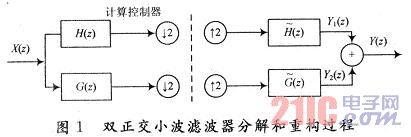

��(du��)��С������(sh��)��Ҫ�������������ԡ��o֧������(du��)�Q�Ժ�ƽ���ԡ������Կ���ʹ׃�Q�o���ࣻ�o֧���t���탞(y��u)���Ŀ��g�ֱ��ʣ���(du��)�Q�Ա��C���c�䌦(du��)��(y��ng)�V��������λ�龀�ԣ�ƽ���Կ��Ԯa(ch��n)���^С��ʧ�档�@��ʹ�xɢ���M(j��n)С��׃�Q�ܵ��ܴ�����ƣ���ˣ��˂����һ�N�p������С��׃�Q�������O(sh��)Ӌ(j��)С���V�������ǻ����p����С��׃�Q��һ�N�pͨ����ȫ�ؘ�(g��u)�V��������˿��Ԍ�(du��)��̖(h��o)�M(j��n)�зֽ��(sh��)�F(xi��n)���_�ؘ�(g��u)�����Ԍ�(du��)��̖(h��o)�ĞV���кܺõ����á�������������׃�Q��Ԫ�ϳ�ӲɘӺͷ�׃�Q��Ԫ�³�Ӳɘ����ԣ����M(j��n)�ОV�����O(sh��)Ӌ(j��)�r(sh��)���Ԍ��p����С���V�����O(sh��)Ӌ(j��)�ɾ��ж���Y(ji��)��(g��u)���pͨ����ȫ�ؘ�(g��u)�V�������p����С��׃�Q���Կ���ԭʼ��̖(h��o)ͨ�^һϵ�иߵ�ͨ�V�����V������(j��ng)�^��Ӻ����õ��ĽY(ji��)�����ؘ�(g��u)�^���c���෴������ʹ׃�Q�����̖(h��o)�܉���ȫ�ؽ���횝M��Y��n��=x-kX��n�������@��ȡk=1���p����С���V�����ֽ���ؘ�(g��u)�^����D1��ʾ��

�O(sh��)G��z����H��z���քe��ֽ��ͨ����ͨ�V�������²ɘӺ���H��z���V���ȃr(ji��)������H��z2���V����Ȼ���²ɘӣ����ԣ�

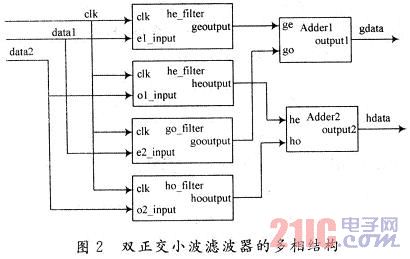

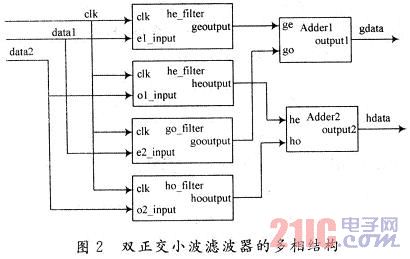

���У�Ge��Go�քe��G��z����ż��(sh��)�(xi��ng)���攵(sh��)�(xi��ng)��He��H���քe��H��z����ż��(sh��)�(xi��ng)���攵(sh��)�(xi��ng)������(j��)ʽ��1����ʽ��2�����Խ����p����С���V�����Ķ���Y(ji��)��(g��u)ģ����D2��ʾ��

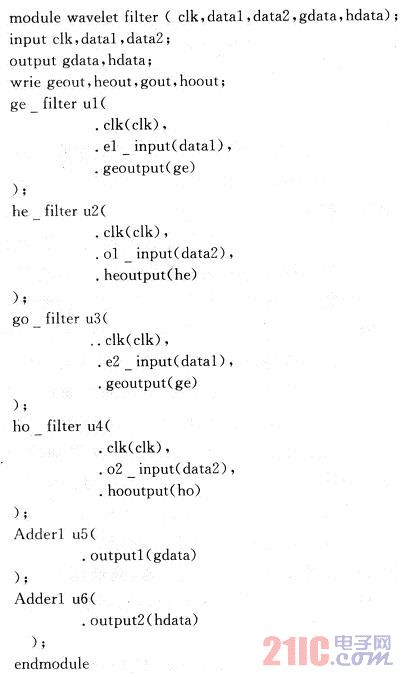

���挦(du��)�p����С���V������VerilogHDL�M(j��n)��플��O(sh��)Ӌ(j��)��

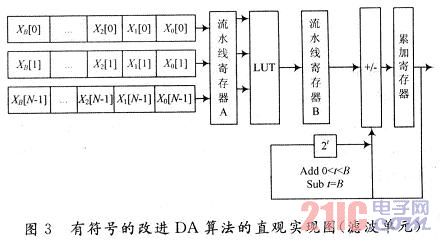

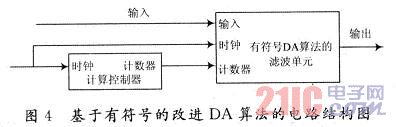

��(du��)���p����С���V�����IJ���Ge��Go��He��Ho�O(sh��)Ӌ(j��)�������О�������ʽ�M(j��n)���O(sh��)Ӌ(j��)��VerilogHDL�О������Z������һ�N�Y(ji��)��(g��u)�����^���Ե��Z�ԣ����Z���Y(ji��)��(g��u)�dz��m�����㷨��(j��)��RTL��(j��)��ģ���O(sh��)Ӌ(j��)����Veril—ogHDL�Z�����О������֞��㷨��RTL�ɷN���㷨��(j��)�����Z���ṩ�ĸ�(j��)�Y(ji��)��(g��u)�܉�?q��)��F(xi��n)�㷨���\(y��n)��ģ�͡�RTL��(j��)��������(sh��)��(j��)�ڼĴ���֮�g������(d��ng)�����̎���������@Щ��(sh��)��(j��)������(d��ng)�����ø��M(j��n)��DA�㷨����D3��ʾ����DA�㷨���һ�ΞV������ҪB�ε��ۼ�Ҳ����B��(g��)�r(sh��)��������һ���\(y��n)�㣬Bλݔ�딵(sh��)��(j��)��λ�������IJ��ұ���LUT���Ĵ�С���ɞV�������A��(sh��)N�Q���ģ�����Ҫ2N��(g��)���ұ��Ԫ�����ϵ��(sh��)N�^�࣬�Æ�(g��)LUT���܉��(zh��)��ȫ�ֲ��҄t�ɰ�ϵ��(sh��)�ֽM�����ò��ֱ������Y(ji��)����ӣ����˺�(ji��n)�ε��U���㷨���ڴ�ϵ��(sh��)ֻ����2�M��ÿ��(g��)��Ԫ��λ�����ɞV������ϵ��(sh��)�������Q���ġ�Ge��Go��He��Ho�Ă�(g��)�V�����mȻ�L(zh��ng)�Ȳ�ͬ����������ͬ���·�Y(ji��)��(g��u)����D4��ʾ��

Ӌ(j��)����������ڿ��ƞV����Ԫ����λ�Ĵ�����λ���ۼ�����ѭ�h(hu��n)���ں�Ӌ(j��)��ݔ������������λ�Ĵ����Ĕ�(sh��)��(j��)ݔ�롣

2 ����VerilogHDL�Z�Ԍ�(sh��)�F(xi��n)���Ϲ���

2.1 ��VerilogHDL�Z���M(j��n)���㷨��ģ

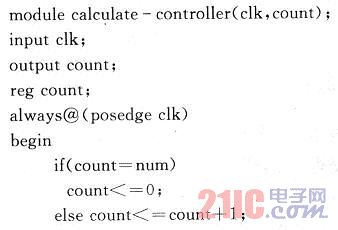

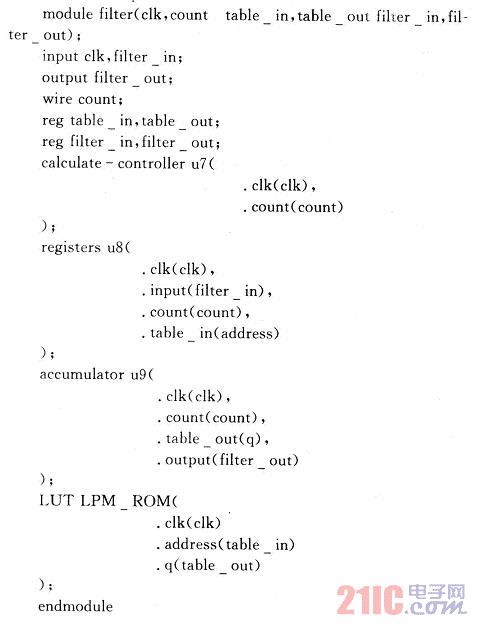

Ӌ(j��)��C(j��)��������veril—ogHDLģ�ͣ�

�Ĵ����M��ÿ��(g��)�Ĵ�����λ��(sh��)��0��1��…��numһ1��

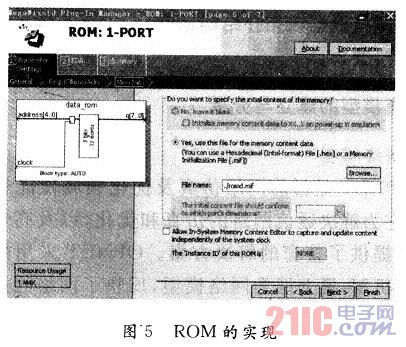

2.2 ����ROM

Quartus��������S�����õ�LPMģ�K�������Ǐ�(f��)�s���(j��)ϵ�y(t��ng)��(g��u)������Ҫ�M�ɲ��֣������cQuartus����ͨ�O(sh��)Ӌ(j��)�ļ�һ��ʹ�ã�ԓ��ʹ��“Tools”�ˆ��µ�MegaWizardPlug—In Manager�����ROM��Ԫ������D5��ʾ��

2.3 ��VerilogHDL�M(j��n)�Д�(sh��)��(j��)����ģ

�V�����Ľ�ģ�^�����£�

3 �(y��n)�C����

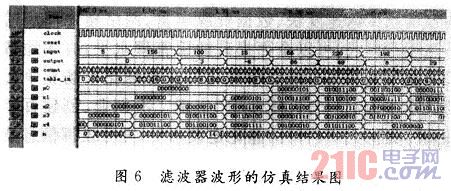

����Altera��˾��Quartus��7.2ܛ����(n��i)�����з�������(du��)�V������VerilogHDLģ���M(j��n)�в��η��棬ͨ�^�������_��Vector Waveform File�Ϳ����_ʼ�����ˡ���D6��ʾ��

ͨ�^Quartus��IJ��η��湦�ܣ���(du��)ݔ��ݔ���M(j��n)�в��η��棬��(du��)��Y(ji��)���M(j��n)�ж���������ͨ�^�r(sh��)��������ܷ����Y(ji��)������(du��)�O(sh��)Ӌ(j��)�M(j��n)���M(j��n)һ�������ơ��ڷ����У�in—put�V����ݔ�딵(sh��)��(j��)��output�V����ݔ�딵(sh��)��(j��)x0��x1��x2��x3��x4����λ�Ĵ����M�мĴ�����count�����Ӌ(j��)��(sh��)����table-in����ˮ���Ĵ��������ýY(ji��)����D6��ʾ����(j��ng)�(y��n)�C������Y(ji��)���͌�(sh��)�H�\(y��n)��Y(ji��)��һ�¡����Ԍ�(du��)�ڴ����(sh��)�B�m(x��)��LTIϵ�y(t��ng)�����Բ������Ϸ����M(j��n)�з�����������Ҳ�о����ԣ���(du��)�ڕr(sh��)׃ϵ�y(t��ng)���Ǿ���ϵ�y(t��ng)���������o�ܞ�����ֻ�m�Ϸ���һ�S׃������(du��)�ڶ�S׃�������o�ܞ������ɲ��à�B(t��i)׃�������������;��_�ȁ��f���@�N�����������Ǻܸߡ�

�M���B�m(x��)LTIϵ�y(t��ng)�кܶ�ȱ�c(di��n)������ͨ�^��(du��)LTIϵ�y(t��ng)�ķ����������B(y��ng)ϵ�y(t��ng)��ģ��������������Ժ��������ϵ�y(t��ng)��������

���P(gu��n)��x:

- ...2012/06/13 11:24������VPN�cOPC����ˮ̎��S�h(yu��n)�̱O(ji��n)��ϵ�y(t��ng)

- ...2012/04/09 16:22�����ڣ֣õ����ⲻ���ཻ��߅���²ü��㷨

- ...2011/11/28 14:39������Virtex-5 FPGA�ĸ��ٴ��Ђ�ݔϵ�y(t��ng)���O(sh��)Ӌ(j��)�c��(sh��)�F(xi��n)[�D]

- ...2011/10/21 15:42������VB�Z�ԵęC(j��)������������ِ�c��(du��)���о�

- ...2011/10/08 13:45������Verilog HDL��CMOS�D���������(q��)��(d��ng)�·

- ...2009/12/18 15:31������VC++�ĵ͉�����ɿ��ԙz�y(c��)ϵ�y(t��ng)

- ...���D��Ԕ����܇�x���屳���܇Ҏ(gu��)��(j��)��ȫ�O(sh��)Ӌ(j��)Ҫ��

- ...��ʹ���а�ȫ���ϵ��W��惦(ch��)��(g��u)����ȫ����܇ϵ�y(t��ng)

- ...������ƫ�ò�־��Ԃ��������^���M(j��n)չ�͑�(y��ng)��

- ...�����¿�˹�y(c��)�u(p��ng)ijƷ�����ܲ����������C(j��)����ƪ

- ...���������ʽ�ضșz�y(c��)���y(c��)��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�(�m(x��))

- ...���������ʽ�ضșz�y(c��)���y(c��)��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�

- ...��RTD�y(c��)��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�

- ...���{(l��n)��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^(q��)�e

- ...��IoT�W(w��ng)�P(gu��n)ƽ�_(t��i)�c��(y��ng)��

- ...������(qi��ng)��ARM DesignStart��ͨ���ƻ�SoC���^�졢�^���L(f��ng)�U(xi��n)֮·

- ...����(sh��)�w�����D(zhu��n)��O2O���}(c��ng)��(ch��)���������ܻ�ˮƽ�ĺ�������

- ...���N܇��LED�(q��)��(d��ng)�����ı��^

- ...���{(l��n)���䌦(du��)�ڶ�ƪ��������ɷ���

- ...��������A�Ƴ��I(l��ng)�ȵğo����(sh��)��(j��)�ɼ���Q����

- ...����ɭ���댧(d��o)�w����Ј�(ch��ng)څ��(sh��)�ğo����늷���

- ...����ɭ���댧(d��o)�w�����܇�����O(sh��)Ӌ(j��)څ��(sh��)�Ľ�Q����

- ...�� ��о��(chu��ng)�����ø�Уδ����܇�˙C(j��)�����O(sh��)Ӌ(j��)��ِ��(b��o)����ʽ����(d��ng)

- ...�� ̽�صڶ����l(w��i)�{(l��n)ɽ������(chu��ng)�¡�������ԇ�(y��n)���g(sh��)Փ����

- ...�� ��2018�Ї�(gu��)�댧(d��o)�w���B(t��i)朴��(hu��)���ڽ��Kʡ�����e��

- ...�� �����}��Ҏ(gu��)����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�(chu��ng)������ܵ�����

- ...�� �ⷨ�댧(d��o)�w��ST����Cinemo��Valens��CES 2018չ��(li��n)����ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a(ch��n)�I(y��)��(chu��ng)�°l(f��)չ�߷�Փ�������ھ����_

- ...�� ����늙C(j��)��(qi��ng)��(sh��)����PCIM����2017չ

- ...�� GPGPU��(gu��)�a(ch��n)������Ї�(gu��)оƬ�a(ch��n)�I(y��)�Ŀհ؎�

- ...�� ��(li��n)�W(w��ng)�a(ch��n)Ʒ�O(sh��)Ӌ(j��)��Wi-Fi�B�ӵ��Ă�(g��)�P(gu��n)�I����

- ...�� �������Ї�(gu��)MEMS���܂������a(ch��n)�I(y��)�l(f��)չ���(hu��)�����ڰ������_�Ļ

- ...�� IAIC���(xi��ng)ِ���[���Ї�(gu��)о����(y��ng)�Ä�(chu��ng)�£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �y(c��)ԇ���g(sh��)

- ...�� ����(g��)�Ј�(ch��ng)�������L(zh��ng)�Ƅ�(d��ng)Molex�ӏ�(qi��ng)��܇�I(l��ng)��İl(f��)չ

- ...�� �Ї�(gu��)�Gɫ����(li��n)�˳������(hu��)���_�ڼ� ���a(ch��n)�W(xu��)���ù�̽�Gɫ�l(f��)չ��ģʽ

- ...�� Efinix® ȫ���(q��)��(d��ng)AI߅��Ӌ(j��)�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r(sh��)���a(ch��n)Ʒ�U(ku��)չ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M(j��n)����(hu��)�����I(l��ng)�ǻ�������

- ...�� ��늮a(ch��n)Ʒ�_�l(f��)���y(c��)ԇ��ӑ��(hu��)��������Դ����(ch��ng)�ɹ��e��

- ...�� Manz���ǿƼ�����댧(d��o)�w�I(l��ng)�� ����弉(j��)�ȳ��ͷ��b�ṩ���W(xu��)���Ƴ̡�Ϳ�������⑪(y��ng)�õ����a(ch��n)�O(sh��)���Q����

- ...�� ������ABITRODE��(d��ng)��늳y(c��)ԇϵ�y(t��ng)���������������Դ

- ...�� ������AFTFϵ��늳y(c��)ԇϵ�y(t��ng)�И�(bi��o)��������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ(f��)�dϵ�y(t��ng)�ɹ����������؈

- ...�� ������A��(gu��)�H��늄�(d��ng)��܇���P(gu��n)�I�����y(c��)�u(p��ng)��ӑ��(hu��)�����[���M(j��n)�y(c��)�u(p��ng)���g(sh��)

- ...�� ��(sh��)��(j��)�ɼ��K��ϵ�y(t��ng)�O(sh��)��

- ...�� ��(ji��n)�x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|(zh��)�J(r��n)�C����܇ϵ�Юa(ch��n)ƷӋ(j��)��

- ...�� ���`˼® �����U(ku��)������� ⁽�ϵ��™ FPGA �a(ch��n)Ʒ ⁽�ϵ�Юa(ch��n)Ʒ�U(ku��)�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_(t��i)�e� (TSMC) 16�{��ˇ��(ji��)�c(di��n)��Ƭ

- ...�� TI��2019��ȫ��(gu��)��W(xu��)������O(sh��)Ӌ(j��)��(j��ng)ِ�C��(ji��ng)��Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C(j��)�@��ȫ���ׂ�(g��)��܇��ȫ�����Եȼ�(j��)(ASIL) ��D���J(r��n)�C

- ...�� ���R��܇�x��BlackBerry������һ����܇