һ���Կɾ��̕r犮a����OmniClock���ṩ�^���OӋ�`���Ժ��S������

�r������ϵ�y�е��P�IԪ�أ������܌�����ϵ�y�ķ����\���������P��Ҫ�����á�OmniClock���ǰ�ɭ���댧�w�Ƴ��Ŀɸ߶ȶ��Ƶ�һ���Կɾ��̕r犮a����ϵ�У����`���Թ����Ј����κοɾ��̕r������������ڿɴ����������֙C���z���C����ӕ�����yʽ��Ӻ����W�Ȍ��V�đ��ã�����С�ߴ硢���ġ��ͳɱ������ƵĴ��_/�������ܵȃ��ݡ�

OmniClockϵ�����Լ��OӋ����

OmniClockϵ��֧�֏�8 kHz��200 MHz������ݔ���l�ʣ��������ζ˕r�ݔ����LVCMOS/LVTTL�������߿��ԽM�ϳ�һ�����ݔ����LVPECL��LVDS��HCSL / CML�������OӋ�ˆT������������w��/����ʎ�����������wϵ�y�ɱ�����NB3H63143G����ͬ�r�ṩһ��50 MHz��125 MHz��48 MHz�r犷քe��CPU�ˡ�����Ӻ�CPU���Ԍ��F�^�����r�(BMC)�㷨����ͬ�r�ṩһ���ζ�50 MHz��һ�����156.25 MHz(LVPECL)�r犵��������ď��s�ɾ���߉����(CPLD)����̫�W������NB3V60113G�����ṩһ��25 MHz�� 0.125 %�ĕr犵��̑BӲ�P(SSD)ģ�K��CPU�ˣ����ṩһ��27 MHz�� 0.5%�ĕr犵�CMOS��������MCLK���r犡�

OE��ݔ��ʹ��

VDDO��ݔ��늉�

��1. ��ɭ���댧�w��ȫϵ��OmniClock�a����

1���ṩ�ɸ߶ȶ��Ƶ��`����

OmniClock�Ǿ��о���ܛ��Clock Cruiser��ȫ���������������õą�������ݔ���l�ʡ�ݔ����͡��������ݔ�����_���Ȳ�ؓ�d��ݡ��Դ늉���ݔ��늉�������ݔ�롢�������_���i��h(PLL)��·���Լ��U�l���õȵȣ���ϵ�y�yԇ�^���У������������g�ɿ����ГQ���ܘ��^�ѵ����ܷ��������⣬�OӋ�ˆT�ɴ惦�_4�����������õ�һ���Կɾ��̃ȴ�(OTPM)��������ݔ��Ҫ�����ƕr��ֱ�ӆ������ã��s�p�_�l�r�g�͜p�͎�档

2������ϵ�y�ɿ���

���þ��w���a���r���̖�����ܕ����Fһϵ�І��}���羀·�岼��Ͳ������ضȺ�늉������ӕr�g�L����Ҫ�~��Ԫ����ؓ�d��ݵȡ�ͨ�^��OmniClock�a����������w���CеʽԪ�����ɜp��ϵ�y���N���ϣ�����ϵ�y�ɿ��ԡ�

3������ϵ�yEMI (늴Ÿɔ_) ��ֵ

�·����Ԫ��֮�g�IJ������ܮa�����ڵ�����EMI��OmniClock�Ȳ�PLL�ṩ��ȫ�ɾ��̵ĔU�l�l���{�ƣ�ͨ�^���N��ͬ�ĔU�l���ÿɽ�Qϵ�yEMI��ֵ�ɔ_���}���U�l���棬�OӋ�ˆT���x��U�l����粻�U�l�����ĔU�l�����ДU�l��ƫ�x�ٷֱ������ĔU�l��0.125%�����ġ�0.125% ����3%�������ДU�l��0.25%������-0.25%��-4%���l���{�ƿ��x30KHz ��130KHz֮�g������ֵ���U�l�{�ƻ���PLL��ݔ����������PLL��·ģʽ�Č�����Ӱ푡��@��Ҫ��ݔ��r��l�ʺ�����ĔU�l�����g�M�Й�⡣

4����ʡ���g�����ͳɱ�

����OmniClockʡȥ���w�����w��ʎ����ؓ�d��ݣ���ʡռ����g���Ķ��������φΣ����͏��s�Ⱥ�ϵ�y�ɱ�����֮���÷dz�С��QFN-16��DFN-8���b���w�e�dz�С���M����ÿ��g�OС�đ�������

5������

������OmniClockϵ�е�һ���P�I���ݣ������L�K�ˮaƷ���yʽ���M�O���늳�ʹ�Õr�g��

OmniClock����USBҕ�lz��C���ƴ��_/����

USBҕ�lz��Cͨ����Ҫ���������r����ڈD����������D��f̎������USB������ģ�K�\���ڲ�ͬ�l�ʣ����Õr犮a�������_���M��ϵ�y�OӋ���ɸ��ƴ��_/���ӣ��ṩ���õIJ����`���ԣ��������Ծ��Ѓ��ݵijɱ��M��ϵ�y������

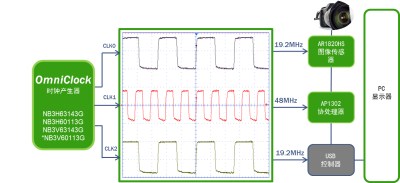

��OmniClock�������Þ�֧��USBҕ�lz��C�����3���l�ʣ��ṩһ��19.2 MHz�r犵�AR1820HS 1800�f���؈D���������һ��48 MHz�r犵�AP1302�D��f̎��������һ��19.2 MHz�r犵�һ��USB��������������w�;��w��ʎ�����ɶ��Ƶ��l�V������ԓϵ�������m���ڌ�EMI���еđ��ö��������������ܡ����`�����Mһ��֧Ԯ�����M�̣���ͨ�^����ܛ����C�ӑB����(OTP)����������С���b�OӋ�����·����s�Ⱥͳɱ���

�D1. OmniClock�ṩUSBҕ�lz��C�����3���l�ʕr�

�����ھW�j�z��Cϵ�y�OӋ�в����^�L�ı�ƽ��|�����ؕr犕��a��EMI�C����ֵ��OmniClock�U�l���ÿɽ�Q�������е�EMI��ֵ���}�������ͳ������ܣ��o����Ӳ������NB3V60113G���������2��ʾ���������÷քe��ȫ�ֱ��ʡ�16M16fps��4k30fps��1080p120fps�ĈD������������w��ʎ�������ʷքe��14.4 fps��15.8 fps��28.8 fps��115.2 fps��NB3V60113G����0%��+/- 3%�İٷֱ��M�ДU�l����������Ȼ���ֲ�׃��

��2. OmniClock�U�l���ò����ͳ�������

�OӋע�����

���кõĕr���̖�������ԱM���pС�����`��б�Ҫ�p����̖���䡣����ϵ��ֻ����Դ�迹����ؓ�d�迹�r���㡣�����Ҫƥ���迹�Ԝp����̖���䡣��ͨ�^��ݔ�����_��������һ���������^���ȵpС�迹���

��ʹ�������ܵ�ϵ�y�Դ����Ӱ푣����N�bһ��0.1 uF��һ��2.2 uF��ȥ����ݵ���·�壬�ұM�����xVDD���_������VDD���_�ľ�·���߾��ͽӵ�ͨ�ב����M���ܱ��Ͷ̡�����VDD���_��������ȥ����ݡ�

�����̖��LVDS���й�ģ�����ƺ͵����Ĺ��Ѓ��ݣ�֧�ֿ����_�P�ٶȣ��ҹ����^���������̖�˜ʵͣ��ȳ���LVDS���_�������Uչ���ṩ�r���̖������LVDS���������Ӷ����c���c朽ӵ����չ��c��

���Y

OmniClockϵ�О鮔ǰ�Ј����κοɾ��̵ĕr������ṩ�^��Ĺ��ܺ��`���ԣ�ԓϵ����������һϵ�о��w���r�ݔ���l���Ԯa��һ·���ݔ��(LVPECL, LVDS, HCSL, CML)��һ·�ζˣ������Ñ����x���l���_��·�ζ�LVCMOSݔ����֧�֏�8 KHz��200 MHz������ݔ���l�ʣ�������w��/����ʎ������ʡռ����e���������wϵ�y�ɱ�����Խ��ȫ���÷������w��ϵ�y�����ƴ��_/���ӣ�����ϵ�y�ɿ��ԣ�ͬ�r����·���OӋ����ʹ�͑��ܝM������ϵ�y���ĵ�Ҫ�Ⱦ��w�s�̽��ڣ��ɶ��ƵĔU�l����߀�����ڌ�EMI���еđ��á�

���P��x:

- ...2017/12/19 15:28�����~˹�댧�w�Ƴ�NFC���܂�����IC�������ڿ��ݡ��ʴ_��һ���ԟo���ض�ӛ䛃x

- ...2014/05/29 10:30��Eppendorf�l���¿�BioBLU® 50cһ����ʹ�������m������

- ...2013/03/11 10:12��Ӣ�w��͵���ӡ�n��˾�y���_�l����һ�����ܴa��LED�@ʾ���İ�ȫ���ܿ�

- ...2012/11/01 09:56��Via Licensing����ᘌ�LTE�������������ڙ��˵�һ�����ڙ��M����Ӌ��

- ...2010/08/05 11:21��һ�����ȍu�رá�Jewel Pump��(ST�cDebiotech)

- ...2010/06/28 10:21���ⷨ�댧�w��ST���cDebiotech�l��һ�����ȍu�رá�Jewel Pump��

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

�aƷ��Ӎ����

��I������

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e