TMS320C6678̎������VLFFT��ʾ

����Ƥ��̽ӑ��TMS320C6678̎������VLFFT��ʾ��ͨ�^����8���̶����cDSP�Ⱥ˵�TMS320C6678̎���������16K-1024K��һ�S�ξ��ȸ��cFFT�㷨�ӱ����z�y��քe�ڲ���1,2,4��8�˕r���Ե��\�Еr�g����ʾ�ĽY���C����C66X DSP�Ⱥ˵ă������ܣ��Լ�TMS320C6678̎��������ƽ�л����������c�Ⱥ˔��������ȵ����ԡ����ĵ���ʾ����FFT�㷨��ԓ�㷨���T���t�W����ͨ�š�܊�º��̘I���_�Լ���ӑ�(�ɔ_�������ɔ_��)���I���б��l�����á�������ʾ�Y���@ʾ�����\�����ʞ�1 GHz��DSP�Ⱥ˞�8���r����TMS320C6678̎��������1024K��FFT�㷨�ӱ�ֻ��Ҫ6.4���롣

TMS320C6678 SoC

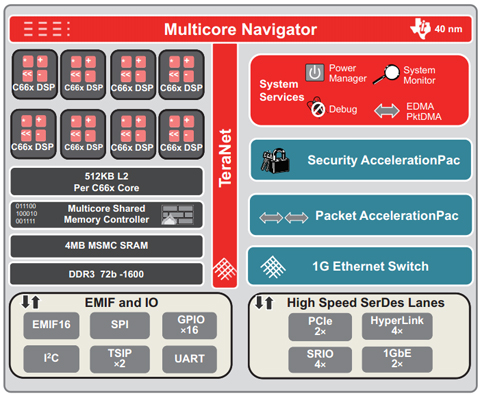

TMS320C6678̎��������8��DSP�Ⱥˣ��ǻ���TI��C66x �̶����cDSP�Ⱥ��Լ� TI���ж�˙����Ą�����KeyStone���܄����ġ����\���ٶ��^�߿��_1.25GHz�����@���ٶ����������M��ÿ��160ǧ�״θ��c�\�㣬����ͨ����r�����ĵ���ܲ���10w��TMS320C6678̎��������ɫ����ÿһ��DSP�Ⱥ˶���512KB�� L2�ȴ棻���⣬8MB��оƬ�ȴ�����4MB�Ĺ���ȴ棬�����@�ɂ��ȴ涼�мm�e�a������DDR3������64λ�ģ���8λ�m�e�a���\���ٶȿ��Ը��_ÿ��1600�ױ��أ�ͬ�r֧�ָ��_8GB���ⲿ�惦��������ȡ�����⣬TMS320C6678���������O����PCle��Serial RapidIO® ��Gigabit Ethernet�Լ�TI��HyperLink���棬�@���������B�ӵ�TI������DSP��ARM�� ARM+DSP̎�����Լ���������FPGA�r�����ṩ���_50Gbps���B���ٶȡ�

�ڱ��ĵ�VLFFT��ʾ�У�TMS320C6678̎�����\���ٶȞ�1GHz��DDR3�����ݔ�ٶȞ�1333MHz��

�Dһ��TMS320C6678��D

VLFFT��ʾ

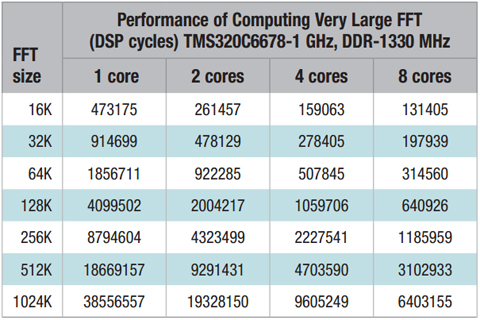

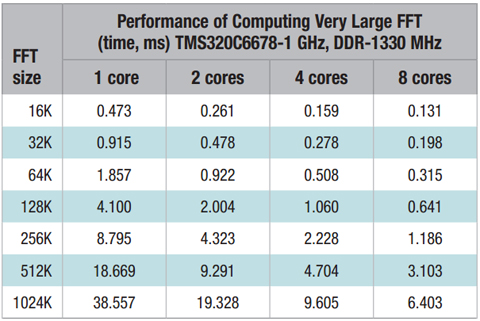

����VLFFT�㷨Ҫ��ݔ��Ĕ��������̎�������ⲿ�惦�����У��ڱ���ʾ�^���У�����ͨ�^DSP�Ⱥ˴�ȡ�������̎�����^�Y��ݔ�����ⲿ�惦���С�ͬ�r���������^����ʼ�K����ѭ�hӋ���͕r�g�y������ʾ�r����TMS320C6678̎�������ò�ͬ�����ăȺˣ�1,2,4��8������Ӌ�㮔FFT��С��ͬ�r�ĽY�����@ЩFFTҎ�������

��16K

��32K

��64K

��128K

��156K

��512K

��1024K

����ʾ�^���У�ͨ�^��Ӌ��ؓ�d�ֲ��������˺���ȫ�������C66X DSP�Ⱥ˸�����Ӌ�������ķ������_������FFT�_���^�����ܡ�ͬ�r�\�û��A�r�g��ȡ�㷨��һ�SVLFFT�㷨����ƵĶ��SFFT�㷨�����_���@�N�������������dz���Ĕ���N�r���ֽ��N=N1*N2����ʽ���ڱ���ʾ�^���У����һ�Sݔ�딵�M�dz��Ͳ���N1��*N2�еĶ��S���M����ʾ��Ȼ��ͨ�^���²��E��Ӌ��FFT��

1��

Ӌ��N2�Д��M��N1�Д��M�в�ͬ��С�r��FFT��

2��

�������D���ӣ�

3��

�惦N2 ����N1�в�ͬ��С�rFFT�㷨�ĽY�����γ�һ��N2*N1�Ķ��S���M��

4��

Ӌ��N1�Д��M��N2�Д��M�в�ͬ��С�r��FFT��

5��

�惦�з����ϵĔ����γ�N2*N1���S���M��

�@���㷨��Takahashi�Q��Hitachi SR8000�ĸ�����ƽ��FFT�㷨��

�ڈ��ж���㷨�r����һ����Ӌ��N2�У��˵Ĕ�������N1��Ҏ���µ�FFT�㷨�����IJ���Ӌ��N1�У��˵Ĕ�������N2��Ҏ���µ�FFT�㷨��0�������ˣ�ؓ؟�c����ʣ�µĸ��ٺ�ͬ��������N1���M��N2���M�Ĵ�С��ÿһ���Ⱥ�Ӌ�������FFT���������ֳɎׂ��^С��ģ�K���m��ÿ����L2 SRAM�ȴ�Ŀ��g��ÿһ�M������ͨ�^�ⲿ�惦���е�DMA �Aȡ��L2 SRAM�ȴ��У�Ȼ��ͨ�^DDR���������ص��ⲿ�惦���С�ÿ���˶��\��2��DMAͨ�����ⲿ�惦����DDR3���̓Ȳ��惦����L2 SRAM�����D��ݔ���ݔ���Ĕ�����

�Y��

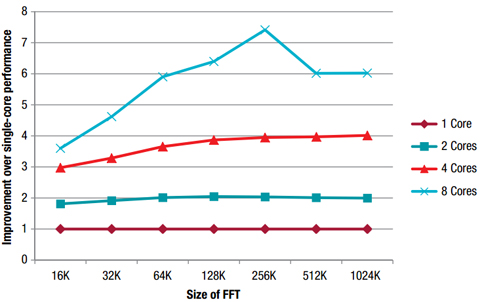

��퓈D��1չʾ��TMS320C6678�u����(TMDSEVM6678LE)�քe��һ��DSP���ں�һ�������λ�r�g���\��FFT���a�ĽY�����������B�£�������Ӌ��ăȺ˔�������һ����ѭ�hӋ���͕��p��һ�롣���ڬF���У����ڴ�����Ϣ�\�е��컨�壬ͬ�r�����ڃȴ��С����Ϣ���ȣ��Ȳ��惦�������@�N��r���y���F�����@�N��r�£������p��ȡ���κ˕r���\��FFT�ĕr�gƽ���p����49.3 %�������_������������ڔ���һ�롣�����ĺ����һ�˕r���\��FFT�ĕr�gƽ���p����72.5%�������ð˺˕rƽ���\�Еr�g�t�p����81.6%��

����һ��FFT�քe��1/2/4/8DSP�˕r���ڼ�����ĽY��

�ɴ��҂����Կ������oՓ���p��߀���ĺˣ��S��FFT�Ĵ�С��16k���ӵ�256k���\�Еr�g�p�ٵķ���ҲԽ��Խ�����ð˺˕r�\�Еr�g�p�ٵķ��ȸ��ӄ��ҡ��@����錦���^С��FFT���˔�Խ�࣬���д��a�������~�����Ӻ˔���������ܵĴ��rҪС�ܶࡣ��ǰ256KB��FFT����������ܷ����Ч������̫���룬���p�˕rֻ�����2�����ĺ˕rҲֻ��4�������ڰ˺˕r���������������ܡ��@�����ڰ˺�̎�픵�����ٶ��h�����ⲿ�惦����ݔ�������ٶȣ��Ķ�ʹ��惦���g���_���ތ��µġ��ڱ���ʾ�У�Ӌ��һ����С��1024k��FFT����һ���f�c��FFT���ڲ���8 ��DSP�Ⱥˣ��\�����ʞ�1GHz�r���\�Еr�g�H6.4���롣

�D�����κ��c����������ϵ�����

�YՓ

�C����������TI��TMS320C6678̎���������һ�����f�c��FFT����1GHz�Ĺ����l���£�8��ͬ�r�\������r�g�H��6.4���롣��˸��ٵ�DSP�Ⱥ���ȫ�����Á����ijЩ���õČ��r�\�㣬�������_����ӑ𠎺��t�W�L�D�ȡ�������^���ٶ�1.25GHz���\��TMS320C6678̎������ͬ�r���ø��ߎ�����DDR3��1600MTPS��Ԓ�������\������r�g�����̡�

���P��x:

- ...2013/02/19 10:01��StreamWIDE�Ƴ����\�I�̞��������Ƅ�ͨӍ��ȫ�˜ʡ�SmartMS™���g

- ...2012/10/12 10:28�����݃x������ Hercules™ TMS570 ARM® ��ȫ���������Դ���������· (PMIC) ��늙C��������܇����ͨ�\ݔ�OӋ���F��Խʽ��

- ...2012/08/13 12:45�����݃x���^�µͳɱ� TMS320C665x KeyStone ��� DSP ����I�W�P�_�l�ˆT�ṩ���ߵ��ܶ��c�ɔUչ��

- ...2011/11/22 10:59�����݃x��(TI)�Ƴ� TMS320C66x ��� DSP ��Ʒ

- ...2011/10/24 16:28�����݃x���Ƴ����� TMS320C66x DSP �����M������ܛ�� ��������֝M���t��Ӱ���_�l�ˆT�����������c����Ӱ���|��������

- ...2011/10/21 14:16��������ĵ��݃x�� TMS320C66x ��� DSP �f�����I�Ԅӻ��_�l�ˆT���F���ܡ��ɔUչ�Լ��`���ԵĿ�ǰ����

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e