����XPS���߿�������Virtex FPGA�İ�֧�ְ�

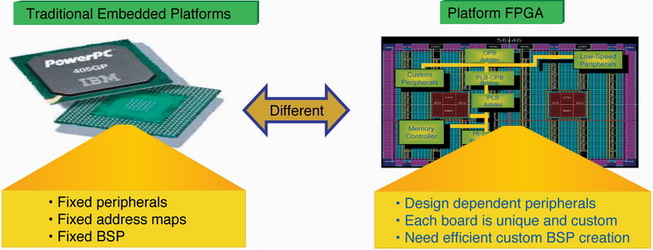

����Ƕ��ʽ̎������ ƽ�_(t��i) FPGA �����ṩǰ��δ�е��`���ԡ����ɶȺ����ܡ�Ŀǰ���چ�(g��)�ɾ���߉�O(sh��)�����_(k��i)�l(f��)�O���(f��)�s�Ҹ߶ȶ��ƻ���Ƕ��ʽϵ�y(t��ng)�ѳɞ���ܡ�

�S��оƬ���ܵIJ������ӣ����ʹ�O(sh��)Ӌ(j��)����ʼ�K��Ч����a(ch��n)���ɞ��˂����R����Ҫ����(zh��n)��Ƕ��ʽϵ�y(t��ng)�_(k��i)�l(f��)���P(gu��n)�I���(d��ng)֮һ���_(k��i)�l(f��)��֧�ְ� (BSP)������ BSP������ʹǶ��ʽܛ����(y��ng)�ó���ɹ��س�ʼ�������c�B�ӵ�̎������Ӳ���YԴ�M(j��n)��ͨ�š����͵� BSP �M����������(d��o)���a���O(sh��)���(q��)��(d��ng)������a�ͳ�ʼ�����a��

��(chu��ng)�� BSP ��һ��(g��)���L(zh��ng)������(f��)���^(gu��)�̣�������̎������(f��)���w��̎���������P(gu��n)�����O(sh��)��ÿ������׃���r(sh��)�����ٴ��M(j��n)�С���(du��) FPGA ���ԣ�Ѹ�ٵ��O(sh��)Ӌ(j��)ѭ�h(hu��n)����ƽ�_(t��i)���`���ԣ���(hu��)ʹ�ù��� BSP ���΄�(w��)�����D�ޣ��D 1�����@һ��r��ʹ�˂����Ҹ���Ч�ع��� BSP �ķ�����

���Č����� Xilinx �ṩ��һ�N��(chu��ng)�½�Q�����������Ժ�(ji��n)�� RTOS BSP �Ą�(chu��ng)���������҂��x���� WindRiver VxWorks ���́�(l��i)�U���@һ��������N(y��n)���ļ��g(sh��)��ͨ�õģ�ͬ���m����֧�� Xilinx® ̎������������������ϵ�y(t��ng)��Q������

���y(t��ng)Ƕ��ʽƽ�_(t��i)

ƽ�_(t��i) FPGA

OPB �ٲ���

�������O(sh��)

�������O(sh��)

PLB-OPB ���

��ͬ��

PLB �ٲ���

�惦(ch��)������

�������O(sh��)

•�̶����O(sh��)

•�̶���ַӳ��

•�̶� BSP

•�����O(sh��)Ӌ(j��)�����O(sh��)

•ÿ��(g��)�嶼�Ǫ�(d��)�صĶ��Ʈa(ch��n)Ʒ

•��Ҫ?ji��ng)?chu��ng)����Ч�Ķ��� BSP

�D 1 – ƽ�_(t��i) FPGA �`����Ҫ��ܛ�� BSP �����^(gu��)�̾��и�Ч��

Xilinx �O(sh��)Ӌ(j��)���̺�ܛ�� BSP ����

Xilinx ̎�������O(sh��)Ӌ(j��)����Ӳ��ƽ�_(t��i)�b�����̺�Ƕ��ʽܛ���_(k��i)�l(f��)���̡��@Щ���̶�ͨ�^(gu��) Xilinx Platform Studio (XPS) �����Թ�����ԓ���ߌ��� Xilinx Ƕ��ʽ�_(k��i)�l(f��)�� (EDK) ��һ���֡�

�O(sh��)Ӌ(j��)ͨ��ʼ���� XPS ���b���c����̎�������c�����B�ӵ���������x��Ӳ��ƽ�_(t��i)�Ϳ�������ϵ�y(t��ng)��ܛ������(sh��)�ˡ�

Platform Studio ��һ��(g��)��Ҫ���c(di��n)�ǣ������Ը���(j��)����(du��)̎���������O(sh��)��Ƕ��ʽ����ϵ�y(t��ng)���x������Á�(l��i)���� BSP��ϵ�y(t��ng)ͨ�^(gu��)Ӳ���O(sh��)Ӌ(j��)�įB����׃���l(f��)չ��ͬ�r(sh��)��BSP �S��ƽ�_(t��i)���l(f��)չ��

�Ԅ�(d��ng)���ɵ� BSP ���x��Ƕ��ʽϵ�y(t��ng)�O(sh��)Ӌ(j��)������������

- �Ԅ�(d��ng)��(chu��ng)���cӲ���O(sh��)Ӌ(j��)��ȫƥ��� BSP

- ʹ���A(y��)�J(r��n)�C�ĽM������ BSP �O(sh��)Ӌ(j��)�e(cu��)�`

- ��������(d��ng)��(y��ng)��ܛ���_(k��i)�l(f��)�������O(sh��)Ӌ(j��)�ߵĮa(ch��n)��

��(chu��ng)������ WindRiver VxWorks �� BSP

Platform Studio ���������� Xilinx Virtex™-II Pro �� Virtex-4 FPGA �е� PowerPC™ 405 ̎�����������O(sh��)�Ķ��� Tornado 2.0.x (VxWorks 5.4) �� Tornado 2.2.x (VxWorks 5.5) BSP�����ɵ� BSP ����ϵ�y(t��ng)���������֧��ܛ��������������(d��o)���a���O(sh��)���(q��)��(d��ng)����� VxWorks ��ʼ����

�� Platform Studio ���x����� PowerPC 405 ̎������Ӳ��ϵ�y(t��ng)��ֻ����ѭ��������(g��)���E������������ VxWorks �� BSP��

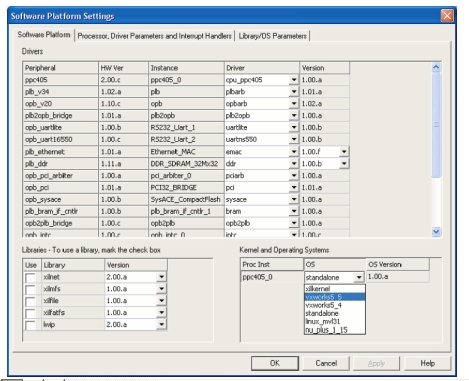

- ʹ��ܛ���O(sh��)�Ì�(du��)Ԓ��Ҋ(ji��n)�D 2���x��Ҫ��ϵ�y(t��ng)ʹ�õIJ���ϵ�y(t��ng)��Platform Studio �Ñ����x�� vxworks5_4 �� vxworks5_5 ������Ŀ��(bi��o)����ϵ�y(t��ng)��

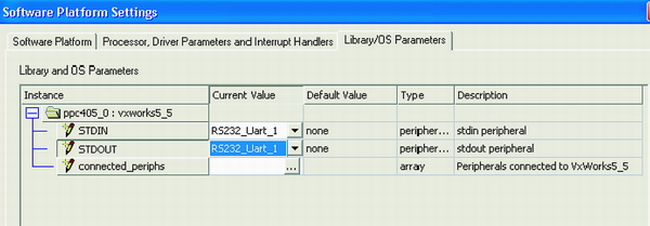

- �x���˲���ϵ�y(t��ng)���D(zhu��n)���Y�ώ�(k��)/����ϵ�y(t��ng)����(sh��)��(bi��o)������D 3 ��ʾ��������(j��)����Ӳ���{(di��o)�� Tornado BSP���������x��ϵ�y(t��ng)�е����� UART ���������(bi��o)��(zh��n) I/O ��������(bi��o)��(zh��n)ݔ��͘�(bi��o)��(zh��n)ݔ�������@��ʹԓ�O(sh��)�䱻���� VxWorks �����_(t��i)������

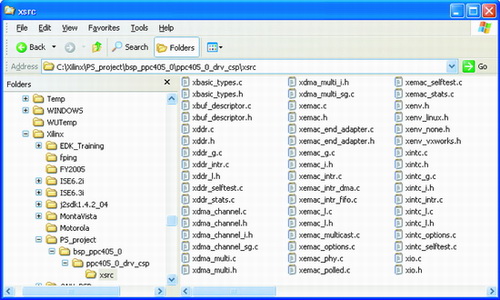

��߀�����x����Щ���O(sh��)�����B�����O(sh��)������Щ�����o�ܼ��ɵ� VxWorks ����ϵ�y(t��ng)�����磬Xilinx 10/100 ��̫�W(w��ng) MAC ���Լ��ɵ� VxWorks ����(qi��ng)�;W(w��ng)�j(lu��)�(q��)��(d��ng)��Enhanced Network Driver �� END)�ӿڡ����ߣ����،���̫�W(w��ng)�����B�ӵ� END �ӿڣ����� VxWorks ��(y��ng)�ó���ֱ���L��(w��n)���� - �x��“���� > �����Y�ώ�(k��)”�� BSP �ˆ��x�(xi��ng)������ Tornado BSP�����ɵ� BSP �c���y(t��ng)�� Tornado BSP ���ƣ�λ�� ppc405_0/bsp_ppc405_0 �µ� Platform Studio �(xi��ng)ĿĿ��У�Ҋ(ji��n)�D 4����

�D 2 – �O(sh��)���x��Ƕ��ʽ����ϵ�y(t��ng)

�D 3 – ���þ��w����ϵ�y(t��ng)�ą���(sh��)

�D 4 – ���ɵ� BSP Ŀ䛽Y(ji��)��(g��u)

ͨ�^(gu��) Platform Studio ���ɵ� Tornado BSP ����һ��(g��) Makefile �ļ������ϣ��ʹ�� Diab ���g�������� Gnu ���g���������������Ĵ��ļ���

Tornado BSP ��ȫ��(d��)���������Ԃ�ݔ?sh��)�����Ŀ�λ�ã��?BSP �Ę�(bi��o)��(zh��n) Tornado ���bĿ䛣�target/config��

���� BSP Ԕ��(x��)��Ϣ

�� XPS ���ɵ����� VxWorks �� BSP �c�����(sh��)���� Tornado BSP ���ƣ�ֻ�� Xilinx �O(sh��)���(q��)��(d��ng)������a��λ��������ͬ���c Tornado ���P(gu��n)�ĬF(xi��n)�ɵ��O(sh��)���(q��)��(d��ng)������aͨ��λ�� Tornado �ֲ�Ŀ䛵� target/src/drv Ŀ��У����� Platform Studio �Ԅ�(d��ng)���ɵ� BSP ���O(sh��)���(q��)��(d��ng)�����aλ�� BSP Ŀ䛱����С�

�D 5 – Tornado 2.x �(xi��ng)Ŀ��VxWorks ��(bi��o)��

���� FPGA ��Ƕ��ϵ�y(t��ng)֮��(d��ng)�B(t��i)��������ɴ�С��e��ԭ����?y��n)���?FPGA ��Ƕ��ϵ�y(t��ng)�������µĻ���ĺ�� IP ���¾��̣��O(sh��)���(q��)��(d��ng)������Ը�׃����˾���Ҫ��(du��)�O(sh��)���(q��)��(d��ng)����Դ�ļ��M(j��n)�и����(d��ng)�B(t��i)�ķ��á��� 4 ���Ԅ�(d��ng)���ɵ� BSP ��Ŀ䛘�(sh��)��Xilinx �O(sh��)���(q��)��(d��ng)��������� BSP ��Ŀ� ppc405_0_drv_csp/xsrc �С�

Xilinx �O(sh��)���(q��)��(d��ng)������ C �P(p��n)�Ј�(zh��)�в��ֲ��ڔ�(sh��)��(g��)Դ�ļ��У��@�c(di��n)��ͬ�ڂ��y(t��ng)�ġ�ͨ���Ɇ�(g��) C header �͈�(zh��)���ļ��M�ɵ� VxWorks �(q��)��(d��ng)�����⣬��(du��)���O(sh��)���(q��)��(d��ng)�����Ъ�(d��)���ڲ���ϵ�y(t��ng)�Ĉ�(zh��)�У����п��x����ه�ڲ���ϵ�y(t��ng)�Ĉ�(zh��)�С�

�(q��)��(d��ng)����IJ���ϵ�y(t��ng)��(d��)�����֑�(y��ng)ͬ�κβ���ϵ�y(t��ng)��̎����һ��ʹ�á����ṩ��һ�N��(y��ng)�ó���ӿ� (API)������ȡ���A(ch��)Ӳ���Ĺ��ܡ��(q��)��(d��ng)����IJ���ϵ�y(t��ng)���ٲ���(du��)�(q��)��(d��ng)�����M(j��n)���{(di��o)����ʹ������� VxWorks ֮IJ���ϵ�y(t��ng)��ʹ�á������д��ж˿�ʹ�õ� Serial IO �(q��)��(d��ng)�������̫�W(w��ng)������ʹ�õ� END �(q��)��(d��ng)����ֻ���ܱ��o�ܼ��ɵ���(bi��o)��(zh��n)����ϵ�y(t��ng)�ӿڵ��(q��)��(d��ng)�����Ҫ�����ϵ�y(t��ng)�����(q��)��(d��ng)����

Xilinx �(q��)��(d��ng)����Դ�ļ����� VxWorks ӳ��(g��u)���ķ�ʽͬ

���P(gu��n)��x:

- ...���D��Ԕ����܇�x���屳���܇Ҏ(gu��)��(j��)��ȫ�O(sh��)Ӌ(j��)Ҫ��

- ...��ʹ���а�ȫ���ϵ��W��惦(ch��)��(g��u)����ȫ����܇ϵ�y(t��ng)

- ...������ƫ�ò�־��Ԃ��������^���M(j��n)չ�͑�(y��ng)��

- ...�����¿�˹�y(c��)�u(p��ng)ijƷ�����ܲ����������C(j��)����ƪ

- ...���������ʽ�ضșz�y(c��)���y(c��)��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�(�m(x��))

- ...���������ʽ�ضșz�y(c��)���y(c��)��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�

- ...��RTD�y(c��)��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�

- ...���{(l��n)��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^(q��)�e

- ...��IoT�W(w��ng)�P(gu��n)ƽ�_(t��i)�c��(y��ng)��

- ...������(qi��ng)��ARM DesignStart��ͨ���ƻ�SoC���^�졢�^���L(f��ng)�U(xi��n)֮·

- ...����(sh��)�w�����D(zhu��n)��O2O���}(c��ng)��(ch��)���������ܻ�ˮƽ�ĺ�������

- ...���N܇��LED�(q��)��(d��ng)�����ı��^

- ...���{(l��n)���䌦(du��)�ڶ�ƪ��������ɷ���

- ...��������A�Ƴ��I(l��ng)�ȵğo(w��)����(sh��)��(j��)�ɼ���Q����

- ...����ɭ���댧(d��o)�w����Ј�(ch��ng)څ��(sh��)�ğo(w��)����늷���

- ...����ɭ���댧(d��o)�w�����܇�����O(sh��)Ӌ(j��)څ��(sh��)�Ľ�Q����

- ...�� ��о��(chu��ng)�����ø�Уδ��(l��i)��܇�˙C(j��)�����O(sh��)Ӌ(j��)��ِ��(b��o)����ʽ����(d��ng)

- ...�� ̽�صڶ����l(w��i)�{(l��n)ɽ������(chu��ng)�¡�������ԇ�(y��n)���g(sh��)Փ����

- ...�� ��2018�Ї�(gu��)�댧(d��o)�w���B(t��i)朴��(hu��)���ڽ��Kʡ�����e��

- ...�� �����}��Ҏ(gu��)����CITE 2019�t���ǻ�δ��(l��i)

- ...�� ����܇�����S��TI���ײ������������ڄ�(chu��ng)������ܵ�����

- ...�� �ⷨ�댧(d��o)�w��ST����Cinemo��Valens��CES 2018չ��(li��n)����ʾ��܇��Ϣ�ʘ�(l��)��Q����

- ...�� ���������·�a(ch��n)�I(y��)��(chu��ng)�°l(f��)չ�߷�Փ�������ھ����_(k��i)

- ...�� ����늙C(j��)��(qi��ng)��(sh��)����PCIM����2017չ

- ...�� GPGPU��(gu��)�a(ch��n)������Ї�(gu��)оƬ�a(ch��n)�I(y��)�Ŀհ؎�

- ...�� ��(li��n)�W(w��ng)�a(ch��n)Ʒ�O(sh��)Ӌ(j��)��Wi-Fi�B�ӵ��Ă�(g��)�P(gu��n)�I����

- ...�� �������Ї�(gu��)MEMS���܂������a(ch��n)�I(y��)�l(f��)չ���(hu��)�����ڰ������_(k��i)�Ļ

- ...�� IAIC���(xi��ng)ِ���[���Ї�(gu��)о����(y��ng)�Ä�(chu��ng)�£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �y(c��)ԇ���g(sh��)

- ...�� ����(g��)�Ј�(ch��ng)�������L(zh��ng)�Ƅ�(d��ng)Molex�ӏ�(qi��ng)��܇�I(l��ng)��İl(f��)չ

- ...�� �Ї�(gu��)�Gɫ����(li��n)�˳������(hu��)���_(k��i)�ڼ� ���a(ch��n)�W(xu��)���ù�̽�Gɫ�l(f��)չ��ģʽ

- ...�� Efinix® ȫ���(q��)��(d��ng)AI߅��Ӌ(j��)�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r(sh��)���a(ch��n)Ʒ�U(ku��)չ����ʮ�f(w��n)߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M(j��n)����(hu��)�����I(l��ng)�ǻ�������

- ...�� ��늮a(ch��n)Ʒ�_(k��i)�l(f��)���y(c��)ԇ��ӑ��(hu��)��������Դ����(ch��ng)�ɹ��e��

- ...�� Manz���ǿƼ�����댧(d��o)�w�I(l��ng)�� ����弉(j��)�ȳ��ͷ��b�ṩ���W(xu��)���Ƴ̡�Ϳ�������⑪(y��ng)�õ����a(ch��n)�O(sh��)���Q����

- ...�� ������ABITRODE��(d��ng)��늳y(c��)ԇϵ�y(t��ng)���������������Դ

- ...�� ������AFTFϵ��늳y(c��)ԇϵ�y(t��ng)�И�(bi��o)��������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ(f��)�dϵ�y(t��ng)�ɹ����������؈

- ...�� ������A��(gu��)�H��늄�(d��ng)��܇���P(gu��n)�I�����y(c��)�u(p��ng)��ӑ��(hu��)�����[���M(j��n)�y(c��)�u(p��ng)���g(sh��)

- ...�� ��(sh��)��(j��)�ɼ��K��ϵ�y(t��ng)�O(sh��)��

- ...�� ��(ji��n)�x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|(zh��)�J(r��n)�C����܇ϵ�Юa(ch��n)ƷӋ(j��)��

- ...�� ���`˼® �����U(ku��)������� ⁽�ϵ��™ FPGA �a(ch��n)Ʒ ⁽�ϵ�Юa(ch��n)Ʒ�U(ku��)�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_(t��i)�e� (TSMC) 16�{��ˇ��(ji��)�c(di��n)��Ƭ

- ...�� TI��2019��ȫ��(gu��)��W(xu��)������O(sh��)Ӌ(j��)��(j��ng)ِ�C��(ji��ng)��Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C(j��)�@��ȫ���ׂ�(g��)��܇��ȫ�����Եȼ�(j��)(ASIL) ��D���J(r��n)�C

- ...�� ���R��܇�x��BlackBerry������һ����܇