���ֿ���DC��DC׃�Q����ADC���OӋ

DC��DC׃�Q���ЃɷN���Ʒ�ʽ��ģ�M���Ʒ�ʽ�͔��ֿ��Ʒ�ʽ�����y��DC��DC׃�Q��һ�����ģ�M���Ʒ�ʽ���������w�eС�����ĵ͵ȃ��c����������Ӱ푡������ֿ��Ƶ�DC��DC׃�Q������ˇ�����ͭh�������С������㷨��ͨ�^���̌��F�����ڼ��ɣ����ܴ��s�̮aƷ���_�l���ڡ��������ڔ��ֿ��Ʒ�ʽ���@Щ���c������DC��DC׃�Q���õ��˂��ďV���Pע��

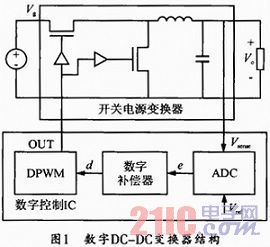

1 DC��DC׃�Q���Y��

���ֿ�������Ҫ��ģ���D�Q��(ADC)�������a����(Digital Compensator)�͔����}�_�����{����(DPWM)�M�ɡ�һ�N���õĔ��ֿ�������D1��ʾ�����·ݔ��늉��c����늉���ADC�M�б��^���D�Q�������Ĕ����`����̖�������a�����t�����`���M���a���õ��o��������̖����DPWM�D�Q�ɕr�g��̖���������·�_�Pͨ�ࡣ

2 ���t��ADC

�˜�CMOS��ˇ��һ��߉�T���ttd�c�Դ늉�VDD߷���@��һ���Pϵ

![]()

���У�K��һ���c������ˇ���P�ij�����Vth��MOS�������ֵ늉�����VDD����Vth�r��td�ɿ����cVDD�ɷ��ȡ�

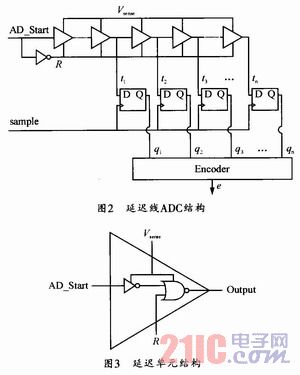

���t��ADC�����t朡��Ĵ����M���g�a�·�M�ɣ��Y����D2��ʾ��һ�����t��Ԫ�M�����t朡�һ�N���е����t��Ԫ�ĽY����D3��ʾ������һ���������cһ������T���õ���ÿ�����t��Ԫ����һ��ݔ��ˣ�һ����λ�˺�һ��ݔ���ˡ�

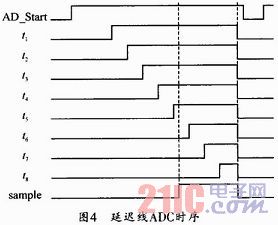

�o��һ���_ʼ��̖AD_Stan����һ���r�g�g����a��һ���ɘ��}�_��̖sample������D�|�l���Ŀ�����̖���ڲɘ���̖��Ч�r��D�|�l����ݔ����̖�M���i�棬��D�|�l����ݔ����̖�����g�a�·�õ��^����`����̖���D4�����t��ADC�ĕr��D�����O�D2��n=8���ڲɘ���̖��Ч�r��AD_Start��̖���Â�����5�����t��Ԫ������q1��q5ݔ����1��q6��q8ݔ����0���ɘ�늉�Խ�����t�r�gtdԽС����̖������Խ�죬ݔ���Ĝض�Ӌ�a�е�1�Ă���Խ�ࡣ�g�a�·�ٌ��ض�Ӌ�a�D�Q������Ҫ�Ķ��M�ƴa�����t��ADC��ͨ�^ݔ���Դ�����t朹�늣��������t����t�r�g�Ĵ�С���_��ݔ��Ĵ�С��

3 ������t��ADC

3��1 ������t��ADC�Y������

���t��ADC�Y�����Σ�����С�������ܹ�ˇ�͜ضȭh��Ӱ푣��Ҳɘ���̖���ⲿ�a�����������·�ď��s�ԣ����Ҳɘ���̖�����t��С��Ӱ�ADC�����ƽ�Ĵ�С��ʹ��ϵ�yݔ����������

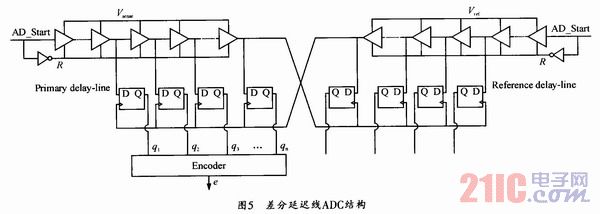

������t���Y���nj����t���Y����һ�N���M���Y���D��D5��ʾ��������t��ADC�Ƀɗlȫͬ�����t朽M�ɣ������t�(Primary delay-line)�ͅ������t�(Reference delay-line)���������t朿ɽ������t朏��ƶ������ɗl������t朹���һ��������̖AD_Start��ʹ�ɗl���t朵Ĺ�����B��ȫ��ͬ��������t朵ăɂ�ݔ��քe�Dzɘ�늉�Vsense�ͻ��ʡ�

늉�Vref��Vsense�С��Vref������늉�Խ�����tԽС��ԭ�����������t����������t朂����꣬���c�����t����B��D�|�l�����_���������t��ϵ�Vsense�M�вɘӡ��@�Ӿ͌��F�ˌ��ɘ�늉��c����늉������^����ͨ�^�g�a�·�õ�ϵ�y��Ҫ�Ĕ����`����̖��

������t��ADC�Ŀ�����̖�ڃȲ��a�����Mһ���������·�Y�������ò����ʽݔ�룬ʹ�òɘ�늉��ͻ���늉�ͬ�r�ܵ��ضȺ�ˇƫ���Ӱ푣��p�������t朵��ӕrƫ�

3��2 ������t��ADC��ģ

�O���t��е����t��Ԫ������N�����t�r�gtd��VDD�ĺ�����td=td(VDD)���t��

���D�Q�r�gTc�Ƿֱ���Vq�����t�r�gtd�Լ����t������б�ʵĺ�����

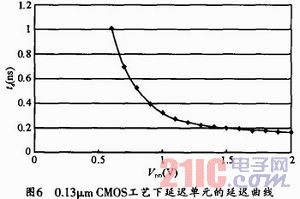

�D6��0��13μm CMOS��ˇ�����t��Ԫ�cVDD���Pϵ������

4 �OӋ�����ͷ���Y��

���t��Ԫ������Ҫ���^�ߣ�����ȫ�����OӋ�����g�a�·������Ҫ���^�ͣ����û��ژ˜ʎ��Ԫ�OӋ�����w�·ʹ��Hsim�M�Д�ģ��Ϸ��档

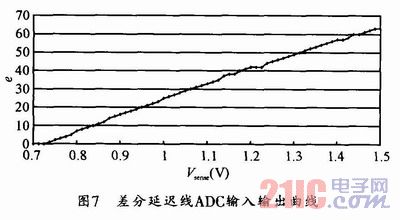

�OӋ�r������늉���1��5V�������l����1��5MHz��ݔ��늉���0��7��1��5V����������ݔ�����g�a��ĽY������6λ������̖e��Vsenseÿ���ӻ�p��12��5mV��e���ӻ�p��“1”����e���^��ֵ��63���D7��0��13μm CMOS��ˇ�²�����t��ADC��ݔ��ݔ�����������Կ�����������t��ADC��ݔ���]�����@ƫ�ƣ���ݔ�댦����ݔ�������Զ����á�

5 �Y���Z

�����ڷ����ˑ����ڔ��ֿ���DC��DC׃�Q���е�ADC�����c�Ļ��A�ϣ��о��˲�����t��ADC�Ľ�ģ�͌��F��ԓ������t��ADC�·�Y�����Σ�����Ҫ�ⲿ�·�a��������̖���ɵ������ֹ�ˇƫ�ԓADC�D�Q���ʺܿ죬���ĵͣ��m�ϑ����ڸ��l����DC��DC׃�Q���С�

���P��x:

- ...2009/07/14 10:23�������l���b�y��Michelson����x�yԇ�_��ʾ���Ĕ��ֿ���

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇