JPEG2000��λƽ�澎�a�Ĵ惦��(y��u)�������O(sh��)Ӌ

����JPEG2000�ăɴ����ģ�K(Ҋ�D1)��С��׃�Q��EBCOT[2](���ڃ�(y��u)���ؔ��c��Ƕ��ʽ�K���a)���\���_�N�ܴ�ռ��(j��)���������a��̎��r�g��һ�����ϡ���ˣ��б�Ҫ�о������Č��F(xi��n)��ʽ��һ����f��ȡܛ�����F(xi��n)��ʽ�������^���Σ�����JPEG2000�ą������ajasper[3]�������r̎���������^���ʹ����Ƕ��ʽϵ�y(t��ng)�ķ�������ʹ��DSP��ARM��ͨ��̎������������Ҳ��ͨ�^ܛ���ķ�ʽ�팍�F(xi��n)���ٶ����������ᘌ��K���a���������c�O(sh��)Ӌ��Ч��Ӳ���Y(ji��)��(g��u)��Ԫ��ֻ���@�ӣ�����ʹJPEG2000�ڌ��r̎���đ�(y��ng)���аl(f��)�]�����á�

����2.�惦��(y��u)���Č��F(xi��n)����

����JPEG2000��Ƕ��ʽ�K���a�ǻ���λƽ��ľ��a���䌦����С��׃�Q���l��ϵ��(sh��)�M�ɵ������^С�Ĵa�K����Сһ����32×32��64×64���a�K�е�ϵ��(sh��)������̖��Ϣ���S������ͬ��(qu��n)ֵ�ķ�����Ϣ��λƽ�澎�a��˼����nj��^��Ҫ����Ϣ���M�о��a��Ҳ���Ǚ�(qu��n)ֵ�^��ķ�����Ϣ�Ⱦ��a���@����Ϻ��m(x��)�Ĵa���M��(Ҋ�D1)����ʹ�^�K�Ĵa���@�Ýu�M��ݔ?sh��)����ԡ?/p>

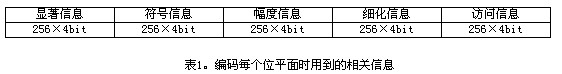

��������(j��)�˜�[1]�����a�^���г����õ���̖�ͷ�����Ϣ�⣬߀��Ҫÿ������λ���@����Ϣ��������Ϣ���L����Ϣ����ˣ�����һ��32×32�Ĵa�K�����aһ��λƽ��r��������Ҫ�惦5×1024λ����Ϣ�����⣬���ھ��a����һ���е�4λ���λ������ͨ����ÿ�K���a��Ϣ�惦��256×4����ʽ(Ҋ��1)��

�������������@�N�惦�Y(ji��)��(g��u)�ǵ�Ч�ģ�������(j��)�˜�[1]�����aһ������λ�����ɂ����E�����Д�ͨ���w�ٺ;��aԭ���������@�ɂ����E�У���Ҫ�L������Ϣ������ǰλ���@������̖�����ȡ��������L����Ϣ���Լ���ǰλ���܇�8������λ���@���ͷ�̖��Ϣ�����ڻ����еľ��a��ʽ�������������ķ����惦��Ϣ��������̖���@����Ϣ�����L��4�惦���t���H��ÿ�ξ��aһ�У���Ҫ�x��ǰһ���a��(ͨ����ÿ4�зQ��һ�����a��)����ǰ���a���ͺ�һ���a���Ĺ�12λ�@���ͷ�̖��Ϣ����������ֻ�����е�6λ�����õģ�����6λ��������Ϣ�����ھ��a�ǻ��ڱ���λ�IJ�������˕��l�����L���惦�^(q��)��ÿ�ξ��aһ�б���x������(y��ng)�ĸ���Ϣλ�����a���һ�Д�(sh��)��(j��)߀Ҫ������(y��ng)�ľ��a��Ϣ�ٴΌ��ش惦�^(q��)�����_�����¾��a��Ϣ��Ŀ�ġ���Ҋ����ȡ����4λ���L�ķ����Ƿdz���Ч�ġ�

�������ԣ������O(sh��)Ӌ��һ�N���������Ĵ惦���������ڴa�K���^����һ�к��^����һ�и�����һ��ȫ0��(sh��)��(j��)(�@�nj��@���ͷ�̖ƽ�����)����(g��u)��34×32�ĉK��Ȼ���ԃ��О�һ�M���������e�惦�ķ�ʽ����A��B��C��B��A����������C��B��A������Ϣ���������K�惦�^(q��)��MEMA��MEMB��MEMC(Ҋ��2)��

�������⣬���@���ͷ�̖��Ϣ���挑��(sh��)��(j��)������(y��ng)�ļĴ���(6×3bit)�r��ҲҪ����(j��)����(y��ng)�ľ��a���M���ГQ�������攵(sh��)���a��(���O(sh��)��һ�����a��ӛ����)������ABC������ż��(sh��)�ľ��a��������CBA(Ҋ��3)�����ң��ı������Կ����������L��MEMA��MEMB��MEMC�ĵ�ַ��̖��׃��Ҳ���M��ͬ�������L��MEMB�ĵ�ַ������L����MEMA�ĵ�ַ�ڏ��澎�a���^�ɵ�ż���a�����^���б��ֲ�׃����ż���a���^�ɵ��澎�a�����^�������L������MEMC����r���ú�MEMA�෴��

������ˣ�����O(sh��)Ӌ����(y��ng)�Ŀ����·�͵�ַ�a(ch��n)���·������@���惦������

����3.Ӳ���ܘ�(g��u)

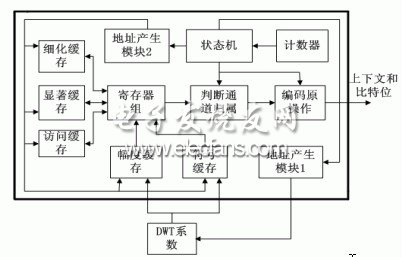

��������(j��)����ķ������������(y��ng)��λƽ�澎�a����Ӳ���ܘ�(g��u)����D2��ʾ�����ܘ�(g��u)ᘌ�32×32�Ĵa�K��

�D2.���ڃ�(n��i)�惞(y��u)��������λƽ�澎�a����Ӳ���ܘ�(g��u)

�����D2�е�λƽ�澎�a����Ҫ�����ׂ����֣�����(n��i)�����棬�Ĵ����M����ַ�a(ch��n)��ģ�K���Д�ͨ���w��ģ�K�����aԭ����ģ�K����B(t��i)�Cģ�K��Ӌ��(sh��)��ģ�K��

������ַ�a(ch��n)��ģ�K�����ɂ�����ַ�a(ch��n)��ģ�K1ؓ؟�a(ch��n)���xȡ�ⲿDWTϵ��(sh��)����ĵ�ַ��̖;��ַ�a(ch��n)��ģ�K2ؓ؟�a(ch��n)���xȡ��(n��i)��5�K����^(q��)�������(y��ng)��ַ��

�����Д�ͨ���w��ģ�K������(j��)��ǰ�Ĵ����M������(y��ng)�ľ��a��Ϣ���Д����λ�Ƿ���ڮ�ǰ�ľ��aͨ����������ڮ�ǰ�ľ��aͨ�����t�M������(y��ng)�ľ��aԭ��������t���^ԓ����λ���^�m(x��)���a��һ������λ��

�������aԭ����ģ�K����4���֣�����ֵ���a����̖���a���������a���γ̾��a��һ��Č��F(xi��n)��ʽ���ò��ұ�팍�F(xi��n)���aԭ�����������O(sh��)Ӌ�о����ýM���·����ʽ�팍�F(xi��n)���@�ӿ�����߮a(ch��n)��CX(���aģʽ)��D(���a����λ)���ٶȡ�

������B(t��i)�Cģ�K�Q�����������a���ľ��a���̣����a��Ҫ�֞�ɂ��A�Σ����A(y��)̎���A�κ�ģʽ�a(ch��n)���A�Ρ��A(y��)̎���A����Ҫ�������5�K����^(q��)���(n��i)�ݵij�ʼ����ģʽ�a(ch��n)���A�΄t�����@�������������ͨ������������M�о��a��ݔ�����aģʽ�o���m(x��)�����g(sh��)���aģ�K����B(t��i)�Cģ�K߀���Ձ���Ӌ��(sh��)����ݔ�����Q����ǰ̎��ʲô��B(t��i)����ÿ��λƽ�澎�a��ɺ����D(zhu��n)���A(y��)̎���A�Σ�������һλλƽ��ķ�����Ϣ���������L������ă�(n��i)�ݡ�

����4.Verilog�O(sh��)Ӌ

�������Ľ��h��Ӳ���ܘ�(g��u)����VERILOG[4]�Z����������ģ�K��bpc.v������ram_block.v��addr_generator.v��fill_ram.v��pass_judge.v��coding_primitive.v��state_machine.v��6 ����ģ�K�����a���̵Č��F(xi��n)ͨ�^����B(t��i)�C�a(ch��n)������(y��ng)��ʹ����̖�����ǰ��ģ�K��������������ɺ���ԓģ�K�a(ch��n)��������ֹ��̖�o����B(t��i)�C���Ķ�ʹ���a�����M����һ���E�������г��˲�������ģ�K�g���ֵĴ��a�����a����ʡ��̖��������һЩ������̖������һЩ��B(t��i)��

����case (cstate)

����������

����gene_layer��begin

����������gene_layer_en = 1;fill_ram_en = 0;pass_judge_en = 0; ������

����if (gene_layer_fin) nstate = fill_ram;else nstate = gene_layer;end

����fill_ram��begin

����������gene_layer_en = 0;fill_ram_en = 1;pass_judge_en = 0; ������

����if (fill_ram_fin) nstate = pass_judge;else nstate = fill_ram;end

����������

����endcase

����5.���Y(ji��)��

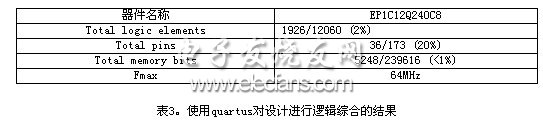

�������O(sh��)Ӌ����modelsim�����M���˹��ܷ��棬ʹ��quartus[6]�����M����߉�C�ϣ��õ��ľC�ϽY(ji��)�����3��ʾ��

����������ʹ��jasperܛ���ͱ�Ӳ�����F(xi��n)�����˜ʈD��(��С512×512�ĻҶȈD��)���a�ĕr�g���^��

����6.�Y(ji��)Փ

��������ͨ�^��JPEG2000�е�λƽ�澎�a���Ĵ惦�����M���˷������O(sh��)Ӌ��һ����Ч�Ĵ惦�Y(ji��)��(g��u)�Լ�����(y��ng)�Ŀ����·���O(sh��)Ӌ����verilog[4]�Z��������ͨ�^quartus[6]ܛ��߉�C�Ϻ��܉���0.1s��(n��i)���һ��512×512�ҶȈD��ľ��a�����a�r�g�H��jasper[3]ܛ�����F(xi��n)������30%���ҡ����ډK���a�������c��ÿ���a�K�ľ��a�����Ǫ����ģ����Բ����M�У����Ҹ���(j��)�C�ϽY(ji��)����ʹ��EP1C12Q240C8��ȫ������һ�KоƬ��(n��i)���ɶ���λƽ�澎�a����IP�ˣ�ÿ���K���a���˿��Բ��Ј�(zh��)�У���ˣ������Mһ����߾��a�����ٶȣ��Ķ�ʹ���r̎��D��ɞ���ܡ����⣬߀���Ԍ��O(sh��)Ӌ���ƞ�ASIC�����^�K�a(ch��n)Ʒ��(y��ng)�õ���(sh��)�a���C���D��O(ji��n)���У����Ј�ǰ����ʮ�֏V韵ġ�

���P(gu��n)��x:

- ...2011/11/11 10:37��TMS320C5409���F(xi��n)JPEG�D�sϵ�y(t��ng)�O(sh��)Ӌ

- ...���D��Ԕ����܇�x���屳���܇Ҏ(gu��)����ȫ�O(sh��)ӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦��(g��u)����ȫ����܇ϵ�y(t��ng)

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑�(y��ng)��

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�(�m(x��))

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^(q��)�e

- ...��IoT�W(w��ng)�P(gu��n)ƽ�_�c��(y��ng)��

- ...��������ARM DesignStart��ͨ���ƻ�SoC���^�졢�^���L�U֮·

- ...�����w�����D(zhu��n)��O2O���}�����������ܻ�ˮƽ�ĺ�������

- ...���N܇��LED�(q��)�ӷ����ı��^

- ...���{���䌦�ڶ�ƪ��������ɷ���

- ...��������A�Ƴ��I(l��ng)�ȵğo����(sh��)��(j��)�ɼ���Q����

- ...����ɭ���댧�w����Ј�څ�ݵğo����늷���

- ...����ɭ���댧�w�����܇�����O(sh��)Ӌڅ�ݵĽ�Q����

- ...�� ��о��(chu��ng)�����ø�Уδ����܇�˙C�����O(sh��)Ӌ��ِ������ʽ����

- ...�� ̽�صڶ����l(w��i)�{ɽ������(chu��ng)�¡�������ԇ�g(sh��)Փ����

- ...�� ��2018�Ї��댧�w���B(t��i)朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ(gu��)����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�(chu��ng)������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ��(li��n)����ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a(ch��n)�I(y��)��(chu��ng)�°l(f��)չ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a(ch��n)������Ї�оƬ�a(ch��n)�I(y��)�Ŀհ؎�

- ...�� ��(li��n)�W(w��ng)�a(ch��n)Ʒ�O(sh��)Ӌ��Wi-Fi�B�ӵ��Ă��P(gu��n)�I����

- ...�� �������Ї�MEMS���܂������a(ch��n)�I(y��)�l(f��)չ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о����(y��ng)�Ä�(chu��ng)�£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g(sh��)

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I(l��ng)��İl(f��)չ

- ...�� �Ї��Gɫ����(li��n)�˳���������_�ڼ� ���a(ch��n)�W���ù�̽�Gɫ�l(f��)չ��ģʽ

- ...�� Efinix® ȫ���(q��)��AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���a(ch��n)Ʒ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I(l��ng)�ǻ�������

- ...�� ��늮a(ch��n)Ʒ�_�l(f��)���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I(l��ng)�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪(y��ng)�õ����a(ch��n)�O(sh��)���Q����

- ...�� ������ABITRODE����늳yԇϵ�y(t��ng)���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y(t��ng)�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y(t��ng)�ɹ����������؈

- ...�� ������A���H��늄���܇���P(gu��n)�I�����y�u��ӑ�������[���M�y�u���g(sh��)

- ...�� ��(sh��)��(j��)�ɼ��K��ϵ�y(t��ng)�O(sh��)��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|(zh��)�J�C����܇ϵ�Юa(ch��n)ƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �a(ch��n)Ʒ ⁽�ϵ�Юa(ch��n)Ʒ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ��(ji��)�c��Ƭ

- ...�� TI��2019��ȫ����W������O(sh��)Ӌ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇