���ü��� DSP �c̎�����Ⱥ˵�Ƕ��ʽ����

���ü��� DSP �c̎�����Ⱥ˵�Ƕ��ʽ����

��������/DSP�ăȺ˰lչ��څ��

Ƕ��ʽ���ð�����̖̎���㷨�c�����㷨���ڶ�N���rǶ��ʽϵ�y���@�ɷN�㷨��ͬ���б���Ĺ��ܣ�����҂����˽�����㷨�c������̖̎���� (DSP) �㷨����Ό��F�������Եġ����֙C�� MP3 �������ȑ����У�Ҫ��Q�����������Ԇ��}�����y�����Ƿքe�� RISC ̎������DSP��̎�������㷨�c��̖̎���㷨�����磬���֙C�У���̖̎������ؓ؟̎����ҕ�l�����еĻ������c����a����������DSP �ܘ��nj��T�OӋ���ڈ�����̖̎���㷨�ģ������̖̎���㷨�� DSP �ϵ� �\��Ч�ʺܸߣ����֙C�еĿ���ܛ���tؓ؟���Р�B�C���������Ñ����桢�I�P����������̖̎�����ܡ�

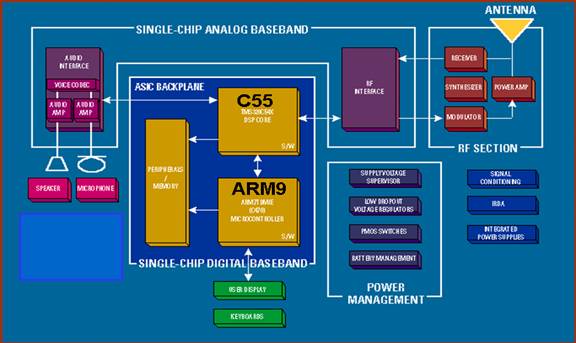

�_�l������̖̎���c�����㷨��Ҫ���@�ɷN�㷨�g���F�������Ե�Ƕ��ʽ���Õr���҂�Ҫ���R�״������e�����f�����҂������摪�û��������s�����B�ӵ�Ƕ��ʽ�O���ϕr��ԓǶ��ʽ�O���DSP/RISC �Ⱥˌ��r�������m�����M�д��a�ֽM(code partitioning)���ஔ���y�����Ҫ�@�ɷN��ͬ�Ⱥˌ��Fͬ��������Ҫ�M�д����Ĺ�����ҕ�l��f�h̎���ȱ����Ƕ��ʽ���Õ����Ӷ��Ⱥ��ϴ��a�ֽM���y�ȣ����Ҵ�������a�ֽM������Ҫ�ɾ����ˆT��ɡ��Բ��õ��݃x�� (TI)TMS320C55x DSP �c ARM RISC ̎�������p�Ⱥ˼ܘ��������f��DSP ������̖̎���΄գ��� ARM 9 �t���п��ƹ��� ����D 1 ��ʾ����

�D 1. ���y���p�Ⱥ� DSP/RISC ̎���ܘ�

��һ�N�������چ��O���м��� DSP �c̎�������҂����� RISC �Ⱥ���������� DSP ��ָ���˷����ۼ�ָ����� DSP �Ⱥ�������ƵĿ���ָ�������ض���ַ�΄յ�ָ����Ķ����F����Ŀ�ġ��{�����P���ߵ�֧�֣��@�N�����ɻ������g����һ���ă��ݣ����ڲ���ϵ�y�σH�\��Ψһ��ԭ�����ã��@�Ӿ��ܺ����OӋ���������ڼ��ɣ����ӿ�aƷ�����M�̡�

�ڂ��yǶ��ʽ�����У��քe����ͨ��̎������������������DSP�Ⱥˁ����ͨ�ù����c��̖̎���㷨�����������ĺ��������ڣ�

- DSP �Ⱥˌ��T�\����̖̎���㷨��Ч���^�ߣ�

- DSP �ܘ�����һϵ�г�Ҋ���ܣ��粢��Ӌ���c�Ƅӡ����ٳ˷��ۼ� (MAC) �\���Լ�Harvard �ܘ��ȣ�֧�ֶ����\���ͬ�r��ȡ��

- DSP̎����ͨ��������RISC�OӋԭ����

- DSP�ܘ�������ż���ý�w�I���ҕ�l��Ӱ���c�Z��̎���ȑ����Լ��������s�c�≺�s���ܵ������\�����ģ�

- DSP ָ��Դ惦���錧��ᘌ��^�V�c�D�Q����̖̎���㷨�Ĉ����M���˾��ă���������֧�������\�㣬DSP ���Ì��üĴ�������ַ��Ԫ���˷��ۼӆ�Ԫ��Ƭ�ϴ惦���ȡ�

ϵ�y���÷ֽM���^���������ڣ�ÿ���Ⱥ˶���Ҫ�Լ����ⲿ�惦����ϵ�y���@�����ӹ��ġ����˿��ƪ����惦����ϵ�y����Ĺ���֮�⣬ͨ��ÿ���Ⱥ�߀Ҫ�����Լ���һ�����O���Ԍ��F̎��Ⱥ˔����Ĵ�ȡ����D1��ʾ��DSP �� ARM �c���Կ��ܻ�����ͬ��һ�����O���惦����ϵ�y���B�����@Ҳ�����ӹ��ģ�����߀���Ӵ����wϵ�yͨ���_�N��

�� RISC �Ⱥ����� DSP ָ��

�� RISC �ܘ��м��� DSP ��Ԫ���H�܉F���ಢ�в���������߀����Ч�ع����YԴ�������O���惦���ȣ�����ˣ������ٶȸ���� RISC �ܘ���DSP�㷨�Ĉ����ٶ�Ҳ����������ˡ�

���^��RISC �ܘ�����ؓ�d���惦ԭ����ָ���ͨ�����^������˕����������ؓ��Ӱ푡����P�O��ĸ��پ��漼�g���^���s�Ҵ���ʹ�ùܾ�̎�����Ķ���Ҫ�^�ߵĕr��l�ʡ����� RISC ��̎�������������� DSP �����c���Ժ�֧�ֳ˷��ۼ�ָ��� DSP �㷨��Ҳ��֧�ֈD���Ӱ��̎���Ȍ��T��Ԫ��

���ڎ� RISC/DSP �p�Ⱥ˵�̎�����܉���Ƀɂ��κ�̎�����Ĺ�������˲�����̎�����gͨ�ŵĆ��}�����ü��ɃȺˣ��҂����� DSP �c�������τӑB�M�д��a�ֽM�����m��ϵ�yҪ���h����׃�����@�Nģʽ���H�܉�ӿ�h���D�Q���������ڟo��������O��惦��������Mһ���������YԴռ�á����⣬�@�N����߀�����ϵ�y�ļ��ɶȣ��@���H�����ڽ����ģ�����߀��ͨ�^�چ��O���ϼ��ɸ���ܶ����F�ɱ����͡��������оƬ�ߴ�s�p��������N���ݡ�

��ǰ�������F�� DSP ̎���������߂�һЩͨ�����ԣ����������� DSP �\��Č��Ô���·������DSP �����ĵ��\������Č���ָ����M������r��惦����ȡ����Ķ����惦�w�c�������Լ�DSP �Č������O�ȡ�

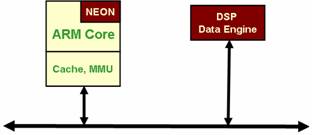

��һ���棬ͨ��̎����Ҳ������Ⱥ��м�������� DSP �Ĺ��ܡ��҂��ɲ��ö�N�������ͨ��̎�������� DSP ���ܡ��OӋ�ˆT�����ӌ��õĆ�ָ�������ָ���Լ��T���ý�w�Uչָ� (MMX)ָ��ȣ�Ҳ�ɞ����ȡ�������ڬF�� CPU�Ⱥˣ��� Hitachi SH-DSP���ϼ�������ڶ��c DSP ̎�����Ĕ���·�����������P�YԴ���cARM ��˾�� NEON �ܘ���ƣ��҂�߀���� CPU ���� DSP�f̎�������OӋ�ˆTҲ�Ʉ������Ⱥ�̎�����Ȼ�ϼܘ���

���м��� DSP �����c���Եļܘ�

NEON SIMD ָ���ܲ���̎�� 16 ��Ԫ�����@������ý�w�� DSP ���á����Pָ���c�Ⱥ�������ϣ���D 2 ��ʾ�����@�N���ɼ��gʹ�҂��ܽyһ�鿴�c ARM �Ⱥ˹����Ĵ惦������r���Ķ���ʹ�ýyһ��ָ���������_�yһ��ƽ�_Ŀ�ˣ��M���������w�����_�l�M�̡�

�@�N�ܘ��� 3G �֙C���ض����ö��Էdz��m�á����@�N���Á��f��DSP �������������ҕ�l���a�Ȍ��T��̎����������������NEON DSP ���ܵ� ARM �Ⱥ˄t��������ҕ�l��a��RISC ̎������t�������Ñ����漰�f�h��̎���ȡ�

�D 2. ARM NEON �ܘ�

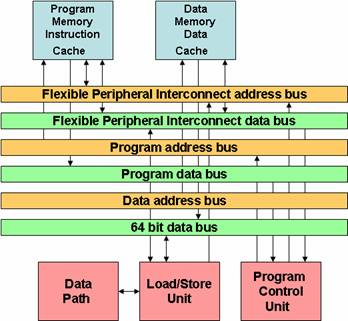

���Ⱥ˼ܘ�����D 3 ��ʾ��������� MCU �� RISC ؓ�d���惦�ͼܘ��c��� DSP �� Harvard �惦���ܘ��Y����һ�𣬵�ַ�������� 32 λ���������c�����惦�������� 64 λ�����Ⱥ˱����������κδ惦�������^�����OӋ�ˆT���ơ��������ܘ����� 32 λ���c����ͨ·��ؓ�d���惦��Ԫ��������Ɔ�Ԫ�ȡ�ԓ�O��ÿ��ѭ�h�܈��ж��_����ָ�����ͨ·ָ�ؓ�d���惦ָ���Լ�ָ����·��ָ����@�m�ϸ�����DSP���õ�����

�D 3. ���Ⱥ˼ܘ�

���P�O��߀֧�ָ��N DSP ��ַģʽ�����а�����ǰ�������ļĴ����g�ӌ�ַ��������ַ��ѭ�h���Ԅ�ģ������ַ��λ���D��ַ�ȡ�λ���D���g���g��FFT�㷨��ݔ��ݔ�������ã��@�dz�Ҋ��DSP����������߀֧�����_�NӲ��ѭ�h��

��֮�����ü��� RISC/DSP ̎����֧���rǶ��ʽϵ�y�ă������ڣ�

- �ڲ�Ӱ�DSP�c���������ܵėl���£����ܘ����������� DSP�c�������Ĺ����c���ԣ�

- �����΄��ГQ����ʹ���ɃȺ�����̓�M̎����һ�ӹ���������DSP �c�������΄��g���F�����ГQ���Еr�H��ׂ��r����ڣ�

- �^���Ƭ�ϴ惦���K��RAM �c ROM�����������ϵ�y���ܲ������ģ�

- ���ɼܘ��o���~���ճ��߉���ֱ�ӿ���Ƭ�����O��

���P��x:

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇