TI C64x+ DSP CACHE һ���Է����c�S�o

���ߣ����݃x�� DSP ���g���ù��̎� ����

ժҪ

�ڸ��N������̖̎��ϵ�y�У�CACHE���V�����ڏ��aCore�c�惦��֮�g���ٶȲ����CACHE��ʹ���^���У����ڲ�ͬ��ʹ惦��֮�g�����Ƿ�һ�µĆ��}���������ط���TI������C64x+ DSPϵ���и���CACHE֮�g����һ���Ԇ��}�Լ�����M��һ���ԾS�o��

1.����

CACHE����Core�͵��ٴ惦��֮�g�Ę��������ڴ��a�͔����ĕr�g�Ϳ��g���P�ԣ��ԉK���λ��Ӳ���������ԄӼ��dCore����Ҫ�Ĵ��a�͔�����������г���͔����Ĵ�ȡ����Core��ɣ�����CACHE���\�ЙC�ƣ�Coreʼ�K�܉�õ��惦�����^�µĔ��������Ǯ����������Ը��Ĵ惦�����ݵIJ������ڕr�����粻��ҪCore���A��ֱ�Ӕ�����ȡ��DMA�����棬�Ϳ��ܳ��F����CACHE�Ĵ��ڶ�����Core����DMA���܉�õ��^�����ĬF��Ҳ����CACHEһ���ԵĆ��}��

2.C64x+ �惦���M���Y��

TI��������C64x���M���˸��M��ʹ�����ܴ���������Q֮��C64x+DSP�ˡ�����C64x+���_�l��DSPоƬ�����в������Խ��Q�W�j��SCR��������B��������SCR�ϵIJ����֞���Master��Slave��Master����Core��EDMA�Լ����и���IO��sRIO����EMAC�����O��Master����ֱ��ͨ�^SCR�l��Slave�Ĕ�����ݔ��Slave����ÿһ��Core�ăȴ棬DDR2����Լ���������ֱ�Ӱl����ݔ�����O��Slave֮�g�Ĕ�����ݔ����Ҫͨ�^DMA�f����ɡ��������C64x+DSP�Ĕ����փ���Ԕ��������SCR�����ú�Master��Slave����r��

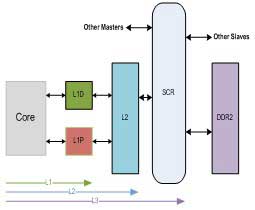

C64x+ϵ�y�Ĵ惦����D��D 1��ʾ���惦�����ֳ�����������һ����L1�����������惦����L1D���ʹ��a�惦��(L1P)���ڶ����Ǵ��a�͔������ô惦����L2�������������ⲿ�惦������Ҫ��DDR2�惦����L1P��L1D��L2��CACHE���ܷքe��������L1P��������L1D��������L2��������ɡ��� 1���Y��C64x+ƽ�_�Ͽ��õ�CACHE��r��

�D 1 C64x+�惦����D

�� 1 C64x+ CACHE����

��ʹ�СLine ��СL1P���a��ֱ��ӳ�䣻�^��32K �ֹ�32 �ֹ�L1D������2·�� �x�����^��32K �ֹ�64 �ֹ�L2���a��������4·���x�������^��256K �ֹ�128 �ֹ�C64x+ƽ�_��L1P�Á��惦���߾�����a��L1D�Á��惦���߾��攵����L1P��L1D��С����32K�ֹ������Էքe����0K��4KB��8KB��16KB����32KB����CACHE������������a���ߔ���RAM������CACHE�IJ��֣��Á�����L2��DDR2�Ĕ�������a������RAM�IJ��֣����Դ惦�P�I�Ĵ��a���ߔ���ʹ��Core�܉��Ժܸߵ��ٶ�

C64x+ƽ�_��L2 �惦�������ڴ惦���a�͔�����L2���^����Է���256K�ֹ�CACHE������DDR2�еĔ�������a��L2�����ಿ������RAM�惦���a�͔�����

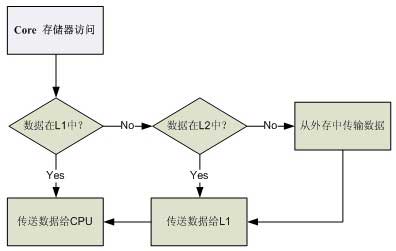

�D 2������Core�L���惦�����ݵIJ������̡����@���L�������У�Core���ڴ惦�����L�������ȏ��xCore�^����һ���惦���_ʼ��������У�Core����ֱ�ӵõ����a/��������t���a/�����������d��ǰ����CACHE�У��Ķ�Core���Եõ�Ҫ̎���Ĵ��a/���������@���ӑB�L���^���У�����CACHE�еă��ݺ���һ���惦���еă��ݿ��ܴ��ڲ�һ�£��@�N˲�B�IJ�һ�²�����Ɇ��}�����ǣ����Core��������Master���ܵõ�����һ�����惦�����ݸ��º�ă��ݣ��͕����FCACHEһ���Ԇ��}��

�D 2 Core�L���惦������

3.CACHEһ���Ԇ��}����

���κΕr�̣�Core��������Master�L���惦���Д����r������CACHE�Ĵ�����ɲ��܉�õ��^�������^�Ĕ������͕����FCACHEһ���Ԇ��}��

��һ���ض��ĕr�g�����ȣ�����CACHE��������һ���惦���еă��ݲ�һ���������ġ����CACHE����������һ�Εr�g�Ȍ����ٴ惦���еă����ԄӰ��\�����ٵ�CACHE���؏�ʹ�á���CACHE�еĿ��g�����m�Ĕ���ռ�õĕr�Ō�CACHE�еă����M��ʧЧ���،��IJ�������ʧЧ���،�֮ǰ��CACHE�еă��ݿ����c�����惦���еă����Dz�һ�µġ��@�N�R�r�ԵIJ�һ���������ģ�����CACHEһ���Ԇ��}���������������������r��

CACHE�������Ǟ������Core��ȡ������Ч�ʣ����Գ��FCACHEһ���Ԇ��}һ���cCore���惦�����L�����P��Core���惦�����L���֞���1.Core�x���a���ߔ�����

2.Core�����a���ߔ�����

���ˣ�CACHE��һ���Ԇ��}�֞�ɂ����Core�xһ���Ԇ��}��Core��һ���Ԇ��}��������ɂ�С���У��քe�������@�ɷN��r��ģ�ͣ�

3.1 Core�xһ����ģ��

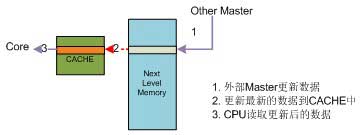

�D 3�o����Core�xһ���Ե�ģ�͡����@��ģ���У�CACHEһ���Ԇ��}�Ĵ���ȡ�Q�ڈD��̓�����^ָʾ�ĵڶ��������ܷ���Core��CACHE�������x����֮ǰ��ɡ�������ܣ��t�����Core�xȡ�Ĕ�����������Master���º�Ĕ���������ԭ��CACHE�еă��ݣ��Ķ�����һ���ԵĆ��}��

�D 3 Core�xһ����ģ��

L1P CACHE��L2�ȴ����DDR2����еĴ��a�M�о��档��Core��һ�Ό�L2����DDR2�еĴ��a�M���x�����ĕr�����ڴ��a����L1P CACHE�У�CAHCEӲ������L2����DDR2�еĴ��a�x��L1P CACHE�С�Core���Եõ��^�µĴ��a��������һ���ԵĆ��}���˺��������Master����L2����DDR2�еĴ��a��Ȼ��Core�ٴ��xȡ�˲��ִ��a�r�����l�F�����Ĵ��a�ѽ�����L1P CACHE�У��˕rCore��ֱ�ӏ�L1P CACHE���xȡ���a������Core���ܵõ��^�µĴ��a���ͳ��F��Core�xһ���ԵĆ��}��

L1D Core�xһ���Ԇ��}��ԭ����L1P��ͬ��ֻ��L1D�������L2����DDR2�еĔ�����

L2 CACHE��DDR2�еĴ��a/�����M�о��棬��Core��һ�Ό�DDR2�еĴ��a/�����M���x�������@�r���a/��������L2 CACHE�У���Ҫ�M��L2 CACHE�ļ��d��Core���Եõ��^�µĴ��a/������֮������Master��DDR2�еĴ��a/�����M�и��ģ�Core���x�˲��ִ��a/�����ĕr��Core�x������L2 CACHE�еă��ݶ�����DDR2���^�µĴ��a/���������Ҳ����Core�xһ���ԵĆ��}��

3.2 Core��һ����ģ��

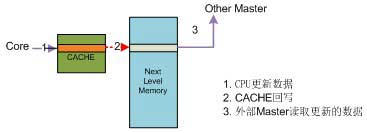

�D 4�o����Core��һ���Ե�ģ�͡����@��ģ���У�CACHEһ���Ԇ��}�Ĵ���ȡ�Q�ڈD��̓�����^ָʾ�ĵڶ��������ܷ�������Master�Ĵ惦�����x����֮ǰ��ɡ�������ܣ����������Master�Ĵ惦�����x���Ĕ�����ԭ���Ĕ���������Core�����^�Ĕ������Ķ�����һ���ԵĆ��}��

�D 4 Core��һ����ģ��

��Core��L2����DDR2�еĴ��a/�����M�Ќ������ĕr��������a/�����ѽ���L1 CACHE�У��µĴ��a/�����������µ�L1 CACHE�С�������Master��L2����DDR2���x���a/�����ĕr��ֱ�ӏ�L2����DDR2���xȡ�����ă��ݣ����L1 CACHE���µĴ��a/����δ�����µ�L2����DDR2�У��t����Master�xȡ�IJ��Ǹ��º�ă��ݣ��͕����FCore��һ���ԵĆ��}��

ͬ�ӣ�Core�����^�Ĵ��a/�����п���ֻ�Ǿ�����L2 CACHE�У�����Master��DDR2���xȡ�ă��ݲ��Ǹ��º�ă��ݣ�ͬ�ӕ����FCore��һ���ԵĆ��}��

3.3 C64x+һ���Է���

��C64x+�ϵ�CACHEһ���Ԇ��}����Ҫ�������ô��a/����������λ���M�з�����������C64x+ƽ�_�ϣ�L1P��L1D��L2�ȴ�ȿ�������CACHE�ֿ�������惦��ʹ�ã���ˣ��ڷ���һ���Ԇ��}�ĕr����Ҫ���]���N��r

Case1.���a��L1P�惦���У�

Case2.���a��L2�惦���У�

Case3.���a��DDR2�惦���У�

Case4.������L1D�惦���У�

Case5.������L2�惦���У�

Case6.������DDR2�惦���С�

����Case1�����ڴ��aֱ����L1P�惦���У�����Ҫ�M��CACHE�����Բ�������һ���ԵĆ��}��

����Case2��Case3���漰��L1P CACHE�����ڴ��a�ĸ����ܷ�Core�x���Ć��}�����a�ĸ��·ֳɃɷN��r��һ��Core���\���^���Ќ����a�M���ģ���������Master�����a���ġ��@�ɷN��r�£���������CACHE�xһ���Ԇ��}����Ҫ��ܛ�����S�o��

����Case4������ֱ����L1D�惦���У� Coreʼ�K�܉��x������Master���µ�L1D�ȴ��еă��ݣ�Core���^�Ĕ���Ҳ�܉�����Masterֱ�ӏ�L1D�ȴ����x�������Բ�������һ���ԵĆ��}��

����Case5��������L2�惦������������ķ�����������CACHE�x�͌�һ���ԵĆ��}����C64x+ƽ�_���@�N��r�µ�һ���Ԇ��}����Ӳ���ԄӾS�o��

����Case6��Ҳ������CACHE�x�͌�һ���ԵĆ��}���@�N��r��Ҫܛ���M��CACHEһ���ԵľS�o��

4.C64x+ CACHEһ���ԾS�o����

���FCACHEһ���Ԇ��}�r�����˱��CCore��������Master���M�Д��������ĕr���܉�õ��^�µĔ�������Ҫ�M��CACHE��һ���ԾS�o������CACHEһ���Ԇ��}�S�o���OӋ�У��ЃɷN̎����ʽ��Ӳ���ԄӾS�o�͑��ó����M�оS�o��

������w�������ώN��r��C64x+ƽ�_������M��CACHEһ���Ԇ��}̎����

4.1 Ӳ���S�o��CACHEһ����

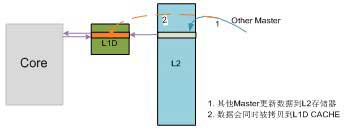

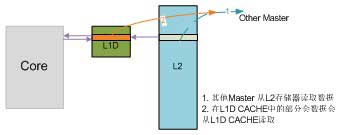

��C64x+ƽ�_�ϣ�Ӳ������Case5����r�Ԅ��M�Д���һ���ԾS�o��������Ҫ�֞��x��������M�У��D 5�͈D 6�քe������Core��L2�ϵĔ����M���x�͌�����r��

�D 5 Core�xL2��������r

�D 6 Core��L2��������r

����MasterҪ��L2�еă����M�и��²����r��L2���������������������ĵ�ַ�Д������ĵ�ַ�Ƿ���L1D CACHE�У������L1D CACHE�У�Ӳ�����Ԅӌ����µĔ�����ؐһ�ݵ�L1D CACHE�С���Core����

���P��x:

- ...2015/01/20 10:57��TI ����Concerto �p��MCU ��PRIME �����ͨ�Ŕ�������������

- ...2014/12/10 15:08��TI NFC �aƷ�������ҕ�еđ���

- ...2011/11/07 09:50����Ό��\��늑����������F� (LiFePO4) 늳�ʹ�õ� TI �迹��ۙ TM 늳����Ӌ�M���{

- ...2011/05/20 10:40�������������T TI �� Codec Engine

- ...2011/05/20 10:32��TI ���� Piccolo™ MCU ֧�ֹ��ܿɿ��� LED ���������I�O��ͼ�늑��� - TInergy ϵ�����£�ʮ����

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇