ʹ��NI VeriStand 2010��(chu��ng)���ֲ�ʽϵ�y(t��ng)

���[

�ֲ�ʽϵ�y(t��ng)�ж�N��ʽ�����磬���c����̎������ͬ��λ��̎��ݔ���ݔ����I/O���ķ���ͨ���Q��ֲ�ʽI/O����һ�������Ǟ��ϵ�y(t��ng)���Ӷ���̎���������\��ֲ�ʽ��������ӑՓ�����ʹ��NI VeriStand 2010��(chu��ng)���ֲ�ʽ̎����I/Oϵ�y(t��ng)�����а������_�l(f��)�ֲ�ʽϵ�y(t��ng)׃�ø�����Ч���������S�����ԡ�

�����w�C����܇���������I(y��)�Ŀ�еĿ���ϵ�y(t��ng)������Ҫ�Ȇ�̎�����忨�͙C�������ṩ�ĸ����Ӌ��������I/O�� �M�бO(ji��n)ҕ���yԇ����档����Ƥ��Ԕ����B����΄�(chu��ng)���ɔUչ���ֲ�ʽ��ͬ��ϵ�y(t��ng)���M�����Ӳ���ڭh(hu��n)��HIL���r�yԇϵ�y(t��ng)������NI VeriStand 2010���������ð���HIL�yԇϵ�y(t��ng)�ڃȵČ��r�yԇ���õļ�����ܛ���h(hu��n)��������NI VeriStand 2010���ԣ��o�茦ܛ���wϵ�Y���M���OӋ�����̺;S�o���Ϳ��Ԅ�(chu��ng)��ϵ�y(t��ng)��

�ֲ�ʽϵ�y(t��ng)����

��ͨ�����Ԍ�����ϵ�y(t��ng)�ֽ�������ͬ�M�����������F(xi��n)ÿ���M����Ӳ����ܛ����Ҫ�ṩ����Ӌ��������I/O�������������ڲ�ͬӲ���ό��F(xi��n)ϵ�y(t��ng)�ĸ����M����

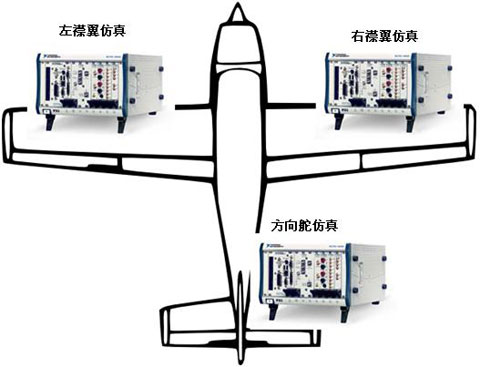

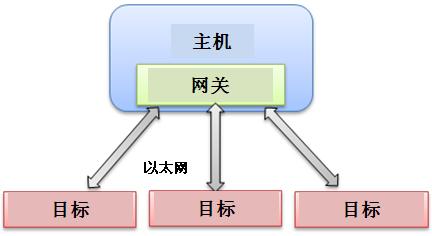

���磬�w�C�Ľ������p��������桢���桢�����ȶ���Ҫ����͜yԇ��������D1��ʾ����ϵ�y(t��ng)�ֽ�����Ӳ���������Ķ�ʹ��ģ�K��������

�D1. �����ö���PXIϵ�y(t��ng)�����w�C�M��

ϵ�y(t��ng)����������

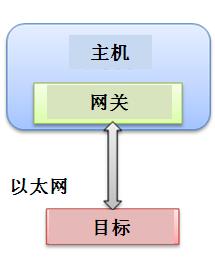

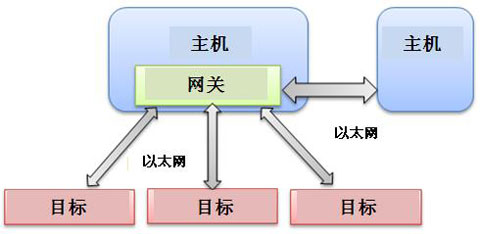

ʹ��NI VeriStand 2010��һ������������ߣ����C��Ӌ��C�������^���Ñ����õ���r�£��cһ����������r��(zh��)��Ŀ���M��ͨ�š�NI VeriStand̎��������Ӌ��C�����C���c���r��(zh��)��Ŀ��֮�g��ͨ�š��D2�o���˰������C��Ŀ�˵ĺ����ؓ�Y����

�D2. �����ؓ�Y��

���C���ں�Ŀ��ͨ�ŵĽM����NI VeriStand Gateway���mȻͨ�Ź������Ԅ���ɵģ�������������ؓ�Y���������Ҫ���

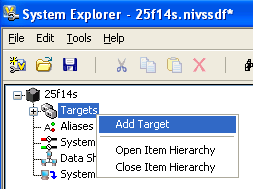

�����Է������NI VeriStand 2010ϵ�y(t��ng)�g�[���Ќ�Ŀ�����ӵ��ؓ�Y���С�

�D3. ��ϵ�y(t��ng)�g�[��������Ŀ��

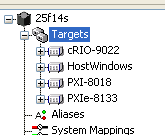

��ϵ�y(t��ng)���x�ļ��������o����Ŀ�ˣ��������Ի�Ͳ�ͬĿ����͡�

�D4. ��ϵ�y(t��ng)���x�ļ�����������Ŀ��

ÿ��Ŀ�����Լ��Č���Ӳ����ܛ�����ã�����Ŀ�˿���ͨ�^���W(w��ng)�P���F(xi��n)����ͽ�����

�D5. ���چ����C�ϲ������Ŀ�˲��M�н���

ͨ�^�c��һ�����C�W(w��ng)�P�M��ͨ�ţ��������CӋ��C�����c��ͬ���ؓ�Y���M��ͨ�š�

�D6. �������C�c����Ŀ���ؓ�Y��

Ҫ����@�c���������Cֻ��Ҫ��NI VeriStand�W(w��ng)�P��ַ���h�����C���ɡ��������ó��ֲ�׃��

�ڷֲ�ʽӋ��C֮�g���픵(sh��)��(j��)

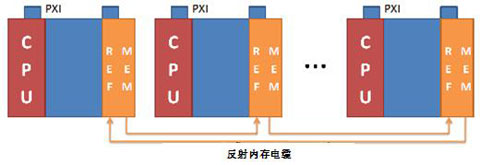

Ҫ�ֲ�ʽϵ�y(t��ng)��ͬ��ϵ�y(t��ng)һ�ӹ����������ϵ�y(t��ng)�M��֮�g���픵(sh��)��(j��)���@����ͬ���ֿ���һ�������P�IҪ�ء�ͨ������ʹ�÷���ȴ�ӿڌ��F(xi��n)��

����ȴ�W(w��ng)�j�nj��r���ؾ���W(w��ng)��LAN����ÿ��Ӌ��C���Ǔ��й���ȴ漯�ϵ��^�±��؏ͱ����@Щ���þW(w��ng)�j�Ǟ����ṩ�ߴ_���ԵĔ�(sh��)��(j��)ͨ�Ŷ����T�OӋ�ġ������ṩ��N�ֲ�ʽ������I(y��)���Ƒ�������ĸ����r���ܡ�����ȴ�W(w��ng)�j�@����ͨ�Ô�(sh��)��(j��)�W(w��ng)�j���Dz�ͬ�����Ƅ��®a������ȫ�����ļ��g���m����Ҫ��_���ԡ����Ό��F(xi��n)��ܛ��ؓ��С�đ��ó���1��

����ȴ��NI VeriStand�ṩ���ڶ���Ŀ��֮�g���픵(sh��)��(j��)�����������ҝM��������ϵ�y(t��ng)�������c�_��������ʹ�÷���ȴ棬����ģ�Ϳ��Էָ��ڲ�ͬ��Ŀ��ϵ�y(t��ng)��ͬ�r��(zh��)�С�ݔ���cݔ����(sh��)ֵͨ�^����ȴ��ڲ�ͬĿ��ϵ�y(t��ng)�Ϲ�����GE Fanuc����ȴ�忨����֧��NI VeriStand 2010��NI VeriStand 2010���S��M������ʹ�÷���ȴ�o�p��(chu��ng)����Ŀ��ϵ�y(t��ng)��

���⣬NI VeriStand 2010����(sh��)��(j��)��Ŀ��֮�g�Ԅӷֲ����ڲ�ͬ����;�����磬���������ü���yԇ���n���\������ҪĿ��B��(sh��)��(j��)��Ŀ��A�ϡ�NI VeriStand 2010��Ŀ��֮�g�Ԅӄ�(chu��ng)���������·�@ȡ��(sh��)��(j��)���@�����ڟo���Ñ����õ���r���Ԅ���ɡ�

�D7�@ʾ�˰�������ȴ�忨�Č���ϵ�y(t��ng)��

�D7. ʹ�÷���ȴ�Ķ����C��

ͬ���ֲ�ʽϵ�y(t��ng)

���OӋϵ�y(t��ng)�r�����]�r���cͬ����������ʮ����Ҫ�ġ�����ֲ�ʽӲ�����M��ͬ����ݔ���ݔ���IJɘӌ���ͬ�r�l(f��)�������⣬�S���r�g�����ƣ�Ư�ƕ�����ϵ�y(t��ng)��һ���M������һ���M���õ�����ɘӣ��M�����������Þ�ͬ�ӵ����ʡ��������������Ŀ�ˣ��@�������}�����磬�ɂ������������̎�ڲ�ͬ�ĕr�g��B(t��i)�����⣬��锵(sh��)��(j��)���ǁ�����ͬ�ĕr�g�c����(sh��)��(j��)ӛ䛺ͷ��������Ɖġ�

ͬ�����A��Ҫ��B������r�Ư�ƺ͕r�ƫ����S�༚��(ji��)��

�ֲ�ʽϵ�y(t��ng)��ͬ������Ӳ��ͬ����ܛ��ͬ�����������x���Ե،�����ϵ�y(t��ng)�cGPS��IRIG���ⲿ�r�g�����M��ͬ����

Ӳ��ͬ��

Ӳ��ͬ����ζ��ϵ�y(t��ng)��ÿ��Ӳ������һ��Ӳ�������r犣����ڶ��r���_ʼI/O�΄ա�ϵ�y(t��ng)�е�ÿ��Ӳ����������ͬ��Ӳ�������r��������Լ��ĕr犣�ÿ��Ӳ��������ͬ�ĕr�g�_ʼ��

��Ҋ��Ӳ�����r��ͬ���΄Ռ�������������(sh��)��(j��)�ɼ��忨��ͬ���ɘӣ��ڸ���(sh��)��(j��)�ɼ�ģ�Mݔ��ͬ�r�����¬F(xi��n)���ɾ����T��У�FPGA���忨��(sh��)��ݔ��PWM��ռ�ձȣ��ڔ�(sh��)���f�ñ���DMM���c�_�P֮�g���֣����ΰl(f��)�����͔�(sh��)�ֻ��x���i�࣬�������l��RF����׃�l�������l��IF����(sh��)�ֻ��x��ͬ����

��������NI PXI�C�䄓(chu��ng)��NI VeriStand�ֲ�ʽϵ�y(t��ng)��PXI��PCI eXtensions for Instrumentation������x��ϵ�y(t��ng)��PCI�Uչ���ǻ���PC�ĈԹ�ƽ�_���ṩ�����ڜy���c�Ԅӻ�ϵ�y(t��ng)�ĸ����ܵͳɱ������Q������PXI�����O�M�����B�˜ʣ�PCI����ӿ����c�Թ̵�CompactPCIģ�K��Eurocard�Cе���b�Y����һ�𣬲������ˌ���ͬ���������P�Iܛ�����ԡ�

�C�����������PXI���壬���а���PCI�����Ͷ��r�c�|�l(f��)������PXIģ�K���x��������10 MHz����ϵ�y(t��ng)�����r犡�PXI�|�l(f��)�����������|�l(f��)�����Ͳی��۾ֲ��������M���˸����r��ͬ���c߅��ͨ�ŵ������Ҳ��pʧ�κ�PCI�ă�(y��u)�c��

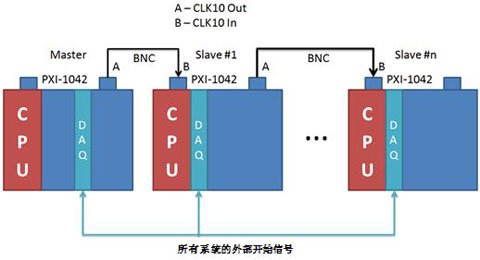

��PXI�C��֮�g���텢���r��^���εķ�����ʹ�ÙC�䱳����CLK10 BNC���^�������еĬF(xi��n)��PXI�C�䶼��BNC���ӡ�ÿ���C����CLK10ݔ�����^��CLK10ݔ����^�����C���CLK10ݔ���c��һ���C���CLK10ݔ�����B���Ϳ��Դ_��ʹ����ͬ�ą����r犡�

Ҫ�����_ʼ�|�l(f��)�������]ʹ��NI��(sh��)��(j��)�ɼ���DAQ���O�䡣һ���C����Ԍ��|�l(f��)��̖������һ������������C�������_ʼ��̖ʹ�á�

�D8 ��Ӳ��ͬ�����õ����ӡ����@�������У�NI PXI-1042���C������BNC��|��CLK10����r犅���������N������PXI�C�䡣���ЙC��������ⲿ�_ʼ��̖����������x�����r�cͬ��ϵ�y(t��ng)�OӋ�˽���C��ͬ���ĸ�����Ϣ��

�D8. ���C���Ӳ��ͬ��

NI VeriStand��һ���C����Ԅ�̎������Ӳ��ͬ����߀���Ԍ�������ɘӕr犺��|�l(f��)��̖������Ŀ���ϡ�

��NI VeriStandϵ�y(t��ng)�g�[���Ќ���(sh��)��(j��)�ɼ��O�����ӵ�ϵ�y(t��ng)���ú��������ڈD9�п���һ����(sh��)��(j��)�ɼ��O������Q�ô��w�@ʾ��NI VeriStand�Ԅ��x�����@���O������C�������(sh��)��(j��)�ɼ��O�䡣����(sh��)��(j��)�ɼ��O������ⲿ�|�l(f��)��̖��ɶ�Ŀ��ͬ����NI VeriStand�چ��C���Ќ��Ĕ�(sh��)��(j��)�ɼ��O���c����(sh��)��(j��)�ɼ��O���M��ͬ�������O�䲻�����ڶ��C��ͬ���С�

�D9. ���w�@ʾ���O�䱻�x����������(sh��)��(j��)�ɼ��O��

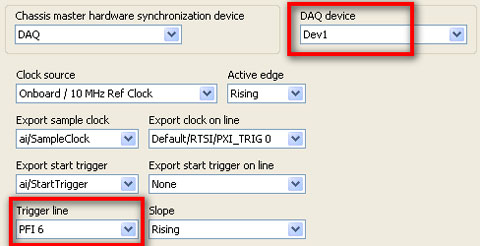

�ڙC������У������Զ�������(sh��)��(j��)�ɼ��O���x���M���|�l(f��)���ژ��νY�����x��C�䡣�����Կ�����D10��ʾ����棬�D�И˳��ˌ����C��Ӳ��ͬ��������Ҫ�ĭh(hu��n)��(ji��)��

�D10. ��PFI 6�C���Ќ����|�l(f��)��

�ڈD10�У��C�����Þ���PFI 6��Dev1�Ќ����|�l(f��)�������Dev1�O���Ӳ���փԌ���PFI 6���ӡ�

�ڄ�(chu��ng)���@Щ���ò����BNC�c�|�l(f��)���ž�֮���Ԍ����������\��VeriStand�Č��r��(zh��)��Ŀ���ρ팍�F(xi��n)Ӳ��ͬ����

�������ʹ�õęC��]��CLK10 BNC���^����������Ҫ���õ�ͬ�����ܣ�������ʹ�ö��r�cͬ���忨��NI-665x�����F(xi��n)��ͬ���ܡ�������Q��ʹ��NI-665x�忨���F(xi��n)�@�����ܣ���Ҫ�_��ÿ��ϵ�y(t��ng)���ö������ˡ�10MHz PLL�����r�cͬ���O�䣬�������Þ錧���10 MHz�r犡�

ܛ��ͬ��

ܛ��ͬ����ζ��ϵ�y(t��ng)�У����@����������NI VeriStand���r���棩����ͬ���a�K������ͬ�Ĉ�(zh��)�Еr犺�һ���_ʼ��̖���F(xi��n)����ͬ�r�g�_ʼ��(zh��)�С�

���m��?sh��)�Ӳ���O����Õr��NI VeriStand���r���汻�OӋ��ʹ��Ӳ�����r���cI/O��HWTSPIO����HWTSPIO��һ�N��(sh��)��(j��)�ɼ�ܛӲ�����ԣ����S��ܛ����(zh��)���i��������Ӳ���r��ϡ���ܛ���i����Ӳ��ֻ�m����ģ�Mݔ�룬��˼�ʹ��ʹ��ģ�Mݔ��ͨ����PXIϵ�y(t��ng)����������Ҫ����һ��ģ�Mݔ��ͨ����

�������Ӳ����������ͬ����ʽ��ģ�Mݔ��ͨ�������F(xi��n)��ÿ�������У�ÿ��Ŀ�˵�NI VeriStand���r����ܛ�����Ԅ�ͬ����

�����r�ͬ��

��һЩ��r�£����HҪ��ϵ�y(t��ng)�M���ͬ����߀Ҫ��ͬ�����ⲿ�r犅������������ͬ��ϵ�y(t��ng)�M���ķ���������Ŀ���c�ֲ�ʽϵ�y(t��ng)�������ֹ���r犺��|�l(f��)��̖�������r�ͬ������ͨ�^���ε،���Ŀ���B�ӵ��ⲿ�r犅������F(xi��n)��

NI VeriStand��Clock 10 Discipline���ӽM��NI VeriStand������Ը���(j��)�ⲿ�����r��M��ͬ�����ⲿ�����r犿�����NI PXI-6

���P��x:

- ...2012/09/04 13:39��ʹ��NI LabVIEW���֙CLCD�M���M���`��ɿ����Ԅӻ��yԇ

- ...2012/08/28 14:20�����ʹ��NI PXI�cLabVIEW����Y�_܇��©��z�yϵ�y(t��ng)

- ...2011/12/30 15:35��ʹ��NI USRP��LabVIEW��o��ͨ�Ō�����OӋ�����`�n��

- ...2011/06/17 11:33��ʹ��NI LabVIEW��PXI�M����Դ�����R�e

- ...2011/06/14 10:49��ʹ��NI VideoMASTER��PXI��(chu��ng)���o��HDMI MIMO��(sh��)��ҕ�l�yԇϵ�y(t��ng)

- ...2011/06/14 10:07��TriQuint Semiconductorʹ��NI PXI��LabVIEW�s�����l���ʷŴ������������r�g

- ...���D��Ԕ����܇�x���屳���܇Ҏ(gu��)����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y(t��ng)

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�(�m(x��))

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^(q��)�e

- ...�� ��о��(chu��ng)�����ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l(w��i)�{ɽ������(chu��ng)�¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B(t��i)朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ(gu��)����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�(chu��ng)������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ��(li��n)����ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I(y��)��(chu��ng)�°l(f��)չ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I(y��)�Ŀհ؎�

- ...�� ��(li��n)�W(w��ng)�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I(y��)�l(f��)չ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä�(chu��ng)�£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İl(f��)չ

- ...�� �Ї��Gɫ����(li��n)�˳���������_�ڼ� ���a�W���ù�̽�Gɫ�l(f��)չ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l(f��)���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y(t��ng)���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y(t��ng)�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y(t��ng)�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� ��(sh��)��(j��)�ɼ��K��ϵ�y(t��ng)�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ��(ji��)�c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇