ALTERA FPGA��̎����ϵ�y(t��ng)�е��ڑ�(y��ng)������

ժҪ�� ALTERA��˾SRAM��ˇ�ɾ���������(y��ng)�ÏV�������������������^���F���ھ���̎������ϵ�y(t��ng)�У�ʹ��̎����ϵ�y(t��ng)�Ĵ惦�����惦���Ô�(sh��)��(j��)����ͨ�^̎��������FPGA���@�N�����������ӳɱ���̎��������(j��)��ͬ�ij���(y��ng)�ã����ò�ͬ�����Ô�(sh��)��(j��)��FPGA�M�����ã�ʹFPGA���F(xi��n)�cԓ��(y��ng)�����P(gu��n)���ض����ܡ�Ԕ����B��̎����ϵ�y(t��ng)���B�Ӻ��εı��Ӵ������÷����ͱ��Ӳ��Ю������÷�����

�P(gu��n)�I�~�� �ڑ�(y��ng)������ FPGA���� ���Ӵ��� ���Ӳ��Ю���

�ɾ���߉������PLD���V����(y��ng)���ڸ��N�·�O(sh��)Ӌ�С����ڲ��ұ����g(sh��)��SRAM��ˇ�Ĵ�Ҏ(gu��)ģPLD/FPGA���ܶȸ����|�l(f��)���࣬�m���ڏ��s�ĕr��߉���电(sh��)����̖̎�����N�㷨���O(sh��)Ӌ���@�����ʹ��SRAM��Ԫ�惦���Ô�(sh��)��(j��)�����Ô�(sh��)��(j��)�Q����PLD��(n��i)�����B���ܣ���׃���Ô�(sh��)��(j��)��Ҳ��׃��������߉���ܡ�SRAM���̕r�g�̣���ϵ�y(t��ng)�ӑB(t��i)��׃PLD��߉���܄�(chu��ng)���˗l����������SRAM�Ĕ�(sh��)��(j��)����ʧ�ģ����Ô�(sh��)��(j��)��횱�����PLD��������ķ���ʧ�惦����(n��i)�����܌��F(xi��n)�ھ��������ã�ICR����

1 �ڑ�(y��ng)�����ã��ӑB(t��i)���ã�

ͬһ�O(sh��)���ڌ��F(xi��n)��ͬ�đ�(y��ng)�Õr��Ҫ��FPGA���F(xi��n)��ͬ�Ĺ��ܡ����ֳֶ�ý�w�O(sh��)�䣬���Ĕz�ֱ����^�ߵ��oֹ�D���գ�����JPEG2000���s��Ҳ�ɂ��ͻ�ӈD����H.263��H.264/AVC�ȡ��μ�ʹ��ܛ�����F(xi��n)�ٶ�������Ҫ���㷨�M�о����ă�(y��u)������ʹ��Ӳ�����F(xi��n)�t�ٶȿ죬���`���Բ��ˣ�����̎������FPGA��Y(ji��)�ρ팍�F(xi��n)�ֳֶ�ý�w�K�ˣ�̎�������F(xi��n)������ƣ�F(xi��n)PGA���F(xi��n)������Ҏ(gu��)�t�\�㡣���⣬�ֳ��O(sh��)���ijЩ��(y��ng)�ã����oֹ�D��ͻ��ҕ�l���s�����ܲ���ͬ�r���F(xi��n)������һƬF(xi��n)PGAͬ�r���F(xi��n)�@Щ���ܣ����H�������s�������y�Ԍ��F(xi��n)��������Ҫ����Ҏ(gu��)ģ��FPGA����ʹ�ò�ͬ�����Ô�(sh��)��(j��)�M�����ã�ʹFPGA�ڲ�ͬ�r�̌��F(xi��n)��ͬ�Ĺ��ܣ��tFPGA�����������@�����ͣ��Ķ������O(sh��)����w�e�����ļ��ɱ���

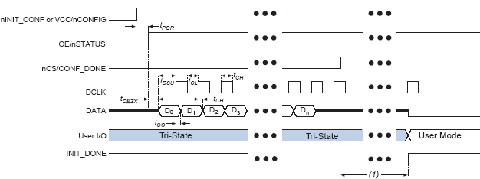

�D 1 APEX FPGA�����Ӵ��У�PS�����Õr��D

ʹ���ڑ�(y��ng)�����Õr�����Ȱё�(y��ng)�÷ּ�������ͬ�r�\�еđ�(y��ng)�÷ֳ�һ�M���ĕr��Ҏ(gu��)�t�\����FPGA���F(xi��n)��������̎�������F(xi��n)����һ��FPGAоƬ�Ķ��������ļ��B�m(x��)�ش����ϵ�y(t��ng)�惦���У��ڳ����(zh��)�Еr��̎�����ь���(y��ng)�ض���(y��ng)�õ����Ô�(sh��)��(j��)�b�d��FPGA�в���ɳ�ʼ������FPGA�M���Ñ�ģʽ����܌��F(xi��n)�ض��Ĺ����ˡ��@�N�������Բ��ø�СҎ(gu��)ģ��FPGA������ʹ�Ì��õİ��F����оƬ����ALTERA��EPC1��EPC2�ȣ����惦���Ô�(sh��)��(j��)��������@���ع�(ji��)ʡϵ�y(t��ng)�ɱ���

ALTERA SRAM��ˇ��FPGA���÷�ʽ��Ҫ�֞�ɴ���������úͱ������á��������÷�ʽ��PLD�����������ò����^�̣����������ⲿ�惦���ͳ�ʼ���^�̣����������÷�ʽ�t���ⲿӋ��C����������������^�̡�����(j��)��(sh��)��(j��)���Ķ����ֿ��Ԍ�PLD�������÷�ʽ�֞鲢�����úʹ������Ãɴ��������ALTERA APEX20KCϵ��������������B�ɷN��̎����ϵ�y(t��ng)���B�Ӻ�����ʹ�÷�������÷�ʽ�����Ӵ������úͱ��Ӳ��Ю������á�

2 ���Ӵ������ã�PS��

���Ӵ������õ���Ҫ�������_���£�

nSTATUS:�����B(t��i)�������Ġ�B(t��i)ݔ������늺�F(xi��n)PGA�����(q��)��ԓ���_�����λ��Ȼ����5��s��(n��i)ጷ�����NSTATUS��(j��ng)�^10k�����������Vcc����������аl(f��)���e�`��F(xi��n)PGA�������͡������û��߳�ʼ���r���������·��nSTATUS���ͣ�F(xi��n)PGA�M���e�`��B(t��i)��

NCONFIG:���ÿ���ݔ�롣���λʹ������λ���ɵ͵��ߵ��λ��׃�������á�

CONF_DONF���p��©�O�_·��������ǰ���������g���B(t��i)ݔ����F(xi��n)PGA�����(q��)�Ӟ�͡��������Ô�(sh��)��(j��)�o�e�`���ղ��ҳ�ʼ���r������_ʼ��F(xi��n)PGA�����Þ����B(t��i)��������������裬���Ԍ���׃?y��u)���ƽ����ʾ���óɹ��������ýY(ji��)���ҳ�ʼ���_ʼ�r��CONF_DONE���B(t��i)ݔ�룺�������·�(q��)��ԓ���_���ͣ��t���t��ʼ��������ݔ����λ�t����������(zh��)�г�ʼ���^�̲��M���Ñ���B(t��i)��

DCLK���r�ݔ�룬���ⲿ��(sh��)��(j��)Դ�ṩ�r犡�

nCE:FPGA����ʹ��ݔ�롣nCE��͕r��ʹ�������^�̡���Ƭ���Õr��nCE���ʼ�K��͡�

nCEO:ݔ���������ڶ�Ƭ��������FPGA������ɺ�ݔ����͡��ڶ�Ƭ��(li��n)���Õr���(q��)����һƬ��nCE�ˡ�

DATA0����(sh��)��(j��)ݔ�룬��DATA0���_�ϵ�һλ���Ô�(sh��)��(j��)��

PORSEL������ݔ�룬�Á��O(sh��)����늏�λ��POR�����ӕr�r�g��

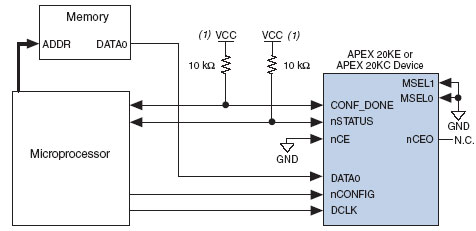

�D 2 ʹ��̎�����ı��Ӵ������÷���

nIO_PULLUP:ݔ�롣���ƽ�r��������ǰ���������gʹ�܃�(n��i)������������裬���Ñ����_����VCCIO��

������ALTERA FPGA������֧�ֱ��Ӵ������á����Ӵ������õ�����D��D1��ʾ�����@�N���÷�ʽ�Л]��������̖�����Õr犵Ĺ����l�ʱ�����������S�ķ������^���l�ʛ]�����ơ������_ʼ���ã����ù��_��JTAG���_���ڵ�bank��VCCINT��VCCIO���蹩늡�FPGA��늺��M���λ��B(t��i)��nCONFIG���Þ���ƽ��ʹFPGA�M���λ��B(t��i)��nCONFIG�ɵ͵��ߵ��λ��׃���������^�̡��������ð��������A�Σ���λ�����úͳ�ʼ������nSTATUS����nCONFIG����ƽ�r������Ó�x��λ��B(t��i)������ጷ�©�O�_·��nSTATUS���_����nSTATUSጷź��ⲿ������ߣ��@�rnSTATUS��nCONFIGͬ�r����ƽ��F(xi��n)PGA�ʂ�������Ô�(sh��)��(j��)�������A���_ʼ���ڴ��������^���У�F(xi��n)PGA��DCLK�������i��DATA0���_�ϵĔ�(sh��)��(j��)���ɹ����յ����Д�(sh��)��(j��)��ጷ�CONF_DONE���_�������ⲿ������ߡ�CONF_DONE�ɵ͵��ߵ��D(zhu��n)׃��־���ýY(ji��)������ʼ���_ʼ���˺�DCLK����ṩ�ׂ����ڵĕr犣����w���ڔ�(sh��)��(j��)�cDCLK���l�����P(gu��n)�����_��Ŀ��оƬ�����_��ʼ������ʼ����ɺ�F(xi��n)PGA�M���Ñ�����ģʽ�����ʹ���˿��x��INIT_DONE��̖���ڳ�ʼ���Y(ji��)����INIT_DONE��ጷţ��ұ��ⲿ������ߣ��@�r�M���Ñ�ģʽ��DCLK��DATA��DATA0���ú������B(t��i)�����ø����õ͡�

�������^���У�һ�����F(xi��n)�e�`��F(xi��n)PGA��nSTATUS���͡�ϵ�y(t��ng)���Ԍ��r�O(ji��n)�y�����R�e���@����̖�������������^�̡�NCONFIG�ɸ�׃�ͣ���׃�߿��������M�����á�һ��nCONFIG���õͣ�nSTATUS��CONF_DONEҲ����FPGA�õ͡���nSTATUS��nCONFIGͬ�r����ƽ�r�������_ʼ��

�D2�Dz���̎������FPGA���Ӵ������÷����ĺ����·�D�������^�̞飺��̎������nCONFIG�õ����ø߁���ʼ�����ã��z�y��nSTATUS׃�ߺ͌����Ô�(sh��)��(j��)����λ�r犷քe�͵�DATA0��DCLK���_���������Ô�(sh��)��(j��)�z�yCONF_DONE�Ƿ�׃�ߣ���δ׃�ߣ��f������ʧ������(y��ng)ԓ�����������^�̡��ڙz�yCONF_DONE׃�ߺ���(j��)�����Ķ��r����(sh��)����һ����(sh��)���ĕr犵�DCLK���_����FPGA��ʼ���ꮅ���M���Ñ�ģʽ�������Ƭ�C����ͬ�����ڣ�DATA0��DCLKʹ��ͬ�����ڵĴ��Д�(sh��)��(j��)ݔ���͕r�ݔ�����@�rֻ��Ҫ���ΰє�(sh��)��(j��)�ֹ�(ji��)�����i�浽�l(f��)�;��_���Ϳ����ˡ���ʹ����ͨI/O��ݔ����(sh��)��(j��)�r��ÿݔ��1�����أ���Ҫ��DCLK�õ����ø߮a(ch��n)��һ�������ء�����ALTERA��˾�փԽo�����·�B�ӈD����Ч��ʹ���˴惦����

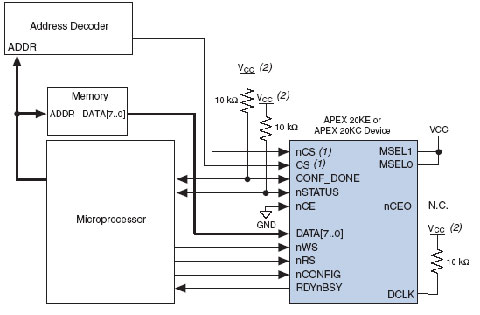

�D 3 ʹ��̎�����ı��Ӳ��Ю��������·

3 ���Ӳ��Ю�������

��ͬ���Ӵ�������һ�ӣ����Ӳ��Ю�������Ҳ���������A�Σ���λ�����úͳ�ʼ�������Ӳ��Ю��������·�D��D3��ʾ����nSTATUS����nCONFIG����ƽ�r������̎�ڏ�λ��B(t��i)��̎������nCONFIG���_�a(ch��n)��һ���ɵ͵��ߵ���׃����FPGA�����á���nCONFIG׃�ߺ�����Ó�x��λ��B(t��i)������ጷ�©�O�_·��nSTATUS���_��F(xi��n)PGA�ʂ�������Ô�(sh��)��(j��)�������A���_ʼ���������A�Σ�̎����FPGA�����惦�����M�Ќ���������̎������ʹƬ�x��Ч��Ȼ���8���ؔ�(sh��)��(j��)�͵�Data[0:7]���_�ϣ������ù��_RDYnBSY�����ƽ����ʾFPGA��æ��̎�����Ô�(sh��)��(j��)��̎�����Ɉ�(zh��)���������ܡ���RDYnBSY���ƽ���g��F(xi��n)PGAʹ�Ã�(n��i)����ʎ���r�̎�����Ô�(sh��)��(j��)����FPGA�ʂ������һ�ֹ�(ji��)�����Ô�(sh��)��(j��)�r�����(q��)��RDYnBSY�����ƽ��̎�����z�y���@һ���ƽ��������һ�ֹ�(ji��)��(sh��)��(j��)�����ù��_�����˹�(ji��)ʡһ���Á�z�yRDYnBSY��I/O�����ɲ����x�惦���ķ����xFPGA������nRS��惦���x��̖����nRS��Ч���g��RDYnBSY��̖���͵���(sh��)��(j��)��D7�ϡ�Ҳ���Բ��z�yRDYnBSY��Ҳ���xFPGA�����εصȴ��ӕrtBUSY(max)+tRDY2WS+tW2SB֮��͌���һ�����Ô�(sh��)��(j��)�ֹ�(ji��)��FPGAÿ̎��һ�ֹ�(ji��)���Ô�(sh��)��(j��)�����l(f��)�F(xi��n)�e�`�͕���nSTATUS���ͣ���ʾ���ó��e��̎�������ԙz�y�@һ�e�`���������M�����á���ͬ���Ӵ�������һ�ӣ�F(xi��n)PGA�����_�����������Ô�(sh��)��(j��)��ጷ�CONF_DONE��̖������ԓ���_���ⲿ����������ߣ���ʾ���ýY(ji��)������ʼ���_ʼ��

4 ���Ô�(sh��)��(j��)�ļ�������

Altera��MAX+PLUS II��Quartus II�_�l(f��)���߿������ɶ�N��ʽ�������ļ������ڲ�ͬ���÷�������ͬĿ�����������Ô�(sh��)��(j��)�Ĵ�С��ͬ�������ļ��Ĵ�Сһ���ɶ��M���ļ����Uչ����.rbf���Q����Altera�ṩ��ܛ�����߲��Ԅ�����.rbf�ļ�����Ҫ��������IJ��E���ɣ�����MAX+PLUS II���g��B(t��i)���x���ļ��ˆ��е�׃�QSRAMĿ���ļ��������׃�QSRAMĿ���ļ���Ԓ��ָ��Ҫ�D(zhu��n)�Q���ļ������x��ݔ���ļ���ʽ��.rbf(Sequential)��Ȼ�����Դ_����

���P(gu��n)��x:

- ...2012/03/30 15:18���t(y��)��Ӱ����㷨�_�l(f��)����[Altera]

- ...2011/10/19 17:05��Altera��Eutecus�l(f��)�������ϵ�һ����FPGA�ό��F(xi��n)��1080p/30fpsҕ�l������Q����

- ...2010/11/25 11:05��The Evolution of Realtime Testing ���r�yԇ����׃

- ...2010/06/11 10:34��ALTERA FPGA��̎����ϵ�y(t��ng)�е��ڑ�(y��ng)������

- ...2009/12/18 14:38��HALT & HASS �ɿ��Ԝyԇ�đ�(y��ng)��

- ...2009/08/31 10:17���Ɖ��Ǟ��ˏ�����HALT�Ɖ�ԇ����ձ��d��

- ...���D��Ԕ����܇�x���屳���܇Ҏ(gu��)����ȫ�O(sh��)ӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦��(g��u)����ȫ����܇ϵ�y(t��ng)

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑�(y��ng)��

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�(�m(x��))

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^(q��)�e

- ...��IoT�W(w��ng)�P(gu��n)ƽ�_�c��(y��ng)��

- ...��������ARM DesignStart��ͨ���ƻ�SoC���^�졢�^���L�U֮·

- ...�����w�����D(zhu��n)��O2O���}�����������ܻ�ˮƽ�ĺ�������

- ...���N܇��LED�(q��)�ӷ����ı��^

- ...���{���䌦�ڶ�ƪ��������ɷ���

- ...��������A�Ƴ��I(l��ng)�ȵğo����(sh��)��(j��)�ɼ���Q����

- ...����ɭ���댧�w����Ј�څ�ݵğo����늷���

- ...����ɭ���댧�w�����܇�����O(sh��)Ӌڅ�ݵĽ�Q����

- ...�� ��о��(chu��ng)�����ø�Уδ����܇�˙C�����O(sh��)Ӌ��ِ������ʽ����

- ...�� ̽�صڶ����l(w��i)�{ɽ������(chu��ng)�¡�������ԇ�g(sh��)Փ����

- ...�� ��2018�Ї��댧�w���B(t��i)朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ(gu��)����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�(chu��ng)������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ��(li��n)����ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a(ch��n)�I(y��)��(chu��ng)�°l(f��)չ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a(ch��n)������Ї�оƬ�a(ch��n)�I(y��)�Ŀհ؎�

- ...�� ��(li��n)�W(w��ng)�a(ch��n)Ʒ�O(sh��)Ӌ��Wi-Fi�B�ӵ��Ă��P(gu��n)�I����

- ...�� �������Ї�MEMS���܂������a(ch��n)�I(y��)�l(f��)չ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о����(y��ng)�Ä�(chu��ng)�£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g(sh��)

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I(l��ng)��İl(f��)չ

- ...�� �Ї��Gɫ����(li��n)�˳���������_�ڼ� ���a(ch��n)�W���ù�̽�Gɫ�l(f��)չ��ģʽ

- ...�� Efinix® ȫ���(q��)��AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���a(ch��n)Ʒ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I(l��ng)�ǻ�������

- ...�� ��늮a(ch��n)Ʒ�_�l(f��)���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I(l��ng)�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪(y��ng)�õ����a(ch��n)�O(sh��)���Q����

- ...�� ������ABITRODE����늳yԇϵ�y(t��ng)���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y(t��ng)�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y(t��ng)�ɹ����������؈

- ...�� ������A���H��늄���܇���P(gu��n)�I�����y�u��ӑ�������[���M�y�u���g(sh��)

- ...�� ��(sh��)��(j��)�ɼ��K��ϵ�y(t��ng)�O(sh��)��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|(zh��)�J�C����܇ϵ�Юa(ch��n)ƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �a(ch��n)Ʒ ⁽�ϵ�Юa(ch��n)Ʒ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ��(ji��)�c��Ƭ

- ...�� TI��2019��ȫ����W������O(sh��)Ӌ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇