ʹ�û��ڈD�ε������C�ϼӿ�FPGA�OӋ�r���Ք�

���y(t��ng)�ľC�ϼ��gԽ��Խ���ܝM�㮔����� 90 �{�����¹�ˇ��(ji��)�c���F�ķdz����ҏ��s�� FPGA �OӋ�������ˡ����}�ǂ��y(t��ng)�� FPGA �C�������ǻ���Դ�� ASIC �ķ��������Ҏ(gu��)�����^(q��)��ȃ�(y��u)�� (IPO,In-place Optimization) �Լ������������R�ľC�� (physically-aware synthesis) �ȡ�Ȼ�����@Щ�� ASIC �Á��ľC���㷨�����m���� FPGA �ij�Ҏ(gu��)�ܘ����A���x�IJ����YԴ��

�^�K�ĽY���ǣ����е����N���y(t��ng) FPGA �C�Ϸ�����Ҫ��ǰ�˾C���c���εIJ��ֲ�������֮�g�M�ж�κĕr���OӋ���ͣ��ԫ@�Õr���Ք����@�����}�Ľ�Q������һ�N���ڈD�εĪ��������C�ϼ��g���܉��ṩһ��ͨ�^�����o�����ľC�ϲ��E������Ҫ ( ������Ҫ���� ) �c���εIJ��ֲ���������OӋ���͡����ң����ڈD�ε������C���ڿ��w�ĕr��ٶȷ�����Ԍ�������� 5% �� 20% �� Synplify Premier ���M FPGA �����C�Ϲ��߾����@��һ�N���ߣ����Tᘌ���Щ�OӋ���s�ĸ߶� FPGA �OӋ���̎������ƣ��������OӋ��Ҫ�����������C�Ͻ�Q������

�������Ƚ�B����Ҫ�Ă��y(t��ng)�C�Ϸ��������f���@Щ�������ڵ����P���}��Ȼ���B���ڈD�ε������C�ϸ����ָ���@�N���g��ΝM�㮔ǰ���M FPGA ���OӋ����

���y(t��ng)�C�Ͻ�Q�������ڵĆ��}

���� 2 �� ASIC ���g��(ji��)�c�Լ������o 80 ���������ǰ���f���·��Ԫ ( ߉�T ) ���P���ӕr�c���B ( �B�Ӿ� ) ���P�ӕr�ı����s 80:20 ��Ҳ�����f�T�ӕr�sռÿ���ӕr·���� 80% ���@��һ�����OӋ���������B��ؓ�dģ�́���Ӌ���B�ӕr�����B��ؓ�dģ���У�ÿ��߉�Tݔ�뱻�x��ij�� �� ��λؓ�d �� ֵ���cij���ض�·�����P���ӕr�����������T�·�ď��Ⱥ��B�Ӿ��ϵĿ������ؓ�d�ĺ�����Ӌ��ó���

��Ƶأ����������o 80 ������� ( ��s���� 1 ���g��(ji��)�c�ĕr�� ) ��һ�� RTL �C�Ϲ����_ʼ���� ASIC �OӋ�еĕr���·��Ԫ���ӕr�c�B���ӕr���߀��ռ������λ�������s�� 66:34 ����ˣ����ڵľC�Ϲ���߀�ǻ����������ӕr��Ӌ��������ʹ�ú��ε��B��ؓ�dģ���M�Ѓ�(y��u)���������·��Ԫ���ӕrռ����������˳��ھC������ʹ�õĻ����B��ؓ�d�ĕr���Ӌ���ʴ_�����εIJ��ֲ�������ͨ�����������^�ٵĎ״η��� ( �� RTL �;C���A��֮�g ) �l�����F�OӋ��

Ȼ�����S��ÿ�����m(x��)���g��(ji��)�c�����룬���B�ӕr�������� ( ���ϣ��� 2005 ����� 90 �{���g���F�Ę˜ʆ�Ԫ ASIC ���f���·��Ԫ�c���B���ӕr�����F���ѽ��ӽ� 20:80) ���@ʹ�þC��������ӕr��Ӌ�c���ֲ������H�ӕr���P��Խ��Խ�͡�

�@����һЩ����Ҫ�Ġ��B�ԣ����C�������ڲ�ͬ�ă�(y��u)������֮�g�x���Լ��ڌ��F���ܵ�������� ( �T����������ĕr���A�y�ļӷ��� ) ֮�g�x�����磬���Oij������һ���ӷ��� ( �Լ������M�� ) ���ض��r��·�����A֪����һЩ ( �r�� ) ԣ�����@�N��r�£��C�Ϲ��߿����x��һ��ռ��оƬ��e�����^С���^���ӷ����汾�����ǣ�����r���Ӌ�c���H�IJ��ֲ��������t��r������^���Ԓ���@��·�������^��dz������@��һ�������ʴ_���ӕr��Ӌ��ζ���C�������^��Ō������_�Č����M�Ѓ�(y��u)����ֻ��������˲��ֲ�������Űl(f��)�F���}���������� ( ��C������ ) ������ǘӣ���Y���ǫ@�Õr���Ք�����Ĺ��������������ӣ�����ǰ�˵���˵��OӋ���ʹΔ���������ˡ�

���˽�Q�@Щ���}���б�Ҫ�˽��ھC���^�����c�OӋ���P���������ԡ���ˣ��S���r�g�����ƣ� ASIC �C�ϼ��g ( �o���� FPGA �C�ϼ��g ) ������һϵ�еķ��� ( ijЩ��r��Ҳ������һЩ���� ) ����������ӑՓ�ĵ�Ҏ(gu��)���� IPO �;����������R�ľC�ϡ�

��Ҏ(gu��)��

���� ASIC �� RTL �C�ϣ���Ҏ(gu��)�����g�������o 90 ������ڳ��F�������ھC�ϼ��g�����Ć�������Ҏ(gu��)���������S�OӋ���������϶��x����^(q��)��ͨ�^�ֹ�����ʹ���Ԅӽ������g�팦�@Щ�^(q��)�֣������OӋ�IJ�ͬ���ַ��䵽�@Щ�^(q��)��

��Ҏ(gu��)���漰������ģ�K�ؾC�Ϻ̓�(y��u)���OӋ��Ȼ�����^�����Ж|�� �� �p�� �� ��һ�� ( ���ڵ�Ҏ(gu��)������ʹ�õľC���㷨���ǻ����B�Ӿ�ؓ�dģ�� ) ���@��ζ����Ҏ(gu��)�����߲��ܰ�ÿ����Ԫ��(y��u)��߉��ֻ��Ӱ�߉ģ�K�IJ��֡����ң��ڶ��x�ϣ���Ҏ(gu��)�����߲���ȫ���Եؿ��]�����YԴ�����OӋ��ȫ�������֮ǰ���������ܜʴ_�������еĕr��·�����@��������ǰ�˺ͺ�˹���֮�g�Ĵ����ĕr���OӋ���͡��M���@�N����������� ASIC �OӋ�ĕr�����ܺͽ����ģ�������Ҫ���OӋ�ď��s�����ͺܸߵČ��I(y��)���gˮ�ʡ�

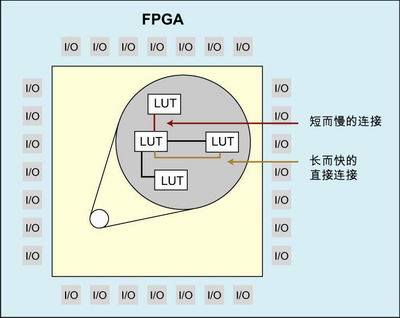

�D 1 �� FPGA �������ܘ�

�����ڣ����� ASIC ��Ҏ(gu��)��������ׂ�ԭ������һ�N�@�Õr�S�Ք��ķ�����Q���������Ć��}����֧�ֻ�������ģ�K���f��׃�����^������Ҏ(gu��)�����ٱ��J����һ�N�䱾���ܫ@�Õr���Ք��ķ�������Ҏ(gu��)����Ȼ��һ�N���õķ�������ֻ�����c�������� ( �������탞(y��u)�� ) �Y�ϵĕr������ã�ʹ�þC�Ϻ��T���W���ĵ�Ҏ(gu��)����Ȼ��Ҫ�dz���Č��T���g��

���� FPGA ���f��ֱ�������o 90 ������ڣ���Ҏ(gu��)�����g߀�]�гɞ��������á�ƽ�����ԣ���һ�� FPGA �OӋ�У��P�I·��һ������^ 3 ���^(q��)������ FPGA һ���õ����OӋ���������ʹ�þC�Ϻ� (�� �T�� ��) �W����(zh��)�е�Ҏ(gu��)������ʹ�� RTL �������^С�ĸ�׃�����܌�����ǰ�����ĵ�Ҏ(gu��)��������֮�|������Q�@�����}�ķ������� RTL ���M�е�Ҏ(gu��)����Ȼ�������˸����ã��@��횺�ij�N��ʽ�����탞(y��u)����Y�ϣ�Դ�� ASIC �������C���㷨�����m���� FPGA �ij�Ҏ(gu��)�ܘ��Լ��A���x�IJ����YԴ��

���փ�(y��u)��

�S����Ҏ(gu��)���� ASIC �I���������u�������������o 90 ������ڣ� IPO ���g�����M���ˏ��� / ����������@�ٴε��漰���r�������Ӌ�ǻ����B�Ӿ�ؓ�dģ�͵ľC�ϡ�

���@�N��r�£����a���ľW�������f�����εIJ��ֲ������档�ڲ��ֲ����ͼ�����ȡ֮���H���ӕr����ע���C�����档�@Щ��ֵ�|�l(f��)���ھC�������е��f����(y��u)��������߉�ؘ��͏��ơ���Y���ǵõ�һ���������ĵ��¾W����Ȼ���@���W�����f�����f�����ֲ������棬�a��һ�����M���OӋ�ؓ䡣

���� IPO �������õ����^��Y������Щ���õ�Ҏ(gu��)�������@�õ�ͨ�����á�Ȼ�����@�N����ͬ�ӿ�����Ҫ��ǰ�˺ͺ�˹���֮�g�M�кܶ���OӋ���͡����һ��� IPO ������һ����Ҫ�Ć��}�nj����ֲ������Ŀ��܌����µ��P�I·�����@��·����ǰһ�η������ǿ������ģ�������һ�����}���ܕ����������Ć��}���@���܌����Ք��Ć��}��

���� FPGA �OӋ������ IPO ���OӋ���̴�s�� 2003 ���_ʼ�ܵ������Pע��Ȼ�����M���@�ӵ������ѽ����ã����Ǖr�@Щ���̲��]����һ�N�����x�ķ�ʽ�õ����ã�������(y��u)���r��·���� IPO ���gͨ����������·���r����ӻ��͕r���Ք�����ȫ���OӋ����Ҫ��ʹ�����ڲ�����֮ǰ�OӋ�汾�@�õijɹ��Ļ��A�ό��OӋ�M�и�׃�Ŀɿ��Y�������ǻ��� IPO �ķ����������ڶ���OӋ����֮�Ϯa����(w��n)���ĽY���������һ�η����Ѓ�(y��u)���P�I·��������һ�η����Юa���µ��P�I·������Ƶأ����Ӽs���Ը��Mһ���^(q��)��ĕr�����ʹ�����ą^(q��)��ĕr����

�����������R�ľC��

��ǰ���M�� ASIC �C�ϼ��g�Ǿ����������R�ľC�ϣ��@�N�C�ϼ��g�ڴ�s 2000 ���_ʼ�ܵ������Pע�������]���H�ļ��g ( �ЎN��ͬ���㷨 ) �������������R�ľC�ϵĻ�����������һ������ɵ��^���нY�ϲ��ֺ;C�ϡ�

�@�� ASIC �I���еČ��`Ч���ܺã�����˽Ⲽ�ֵľC�������ܸ����Ѳ��ֵĆ�Ԫ����߅�� Steiner �Լ� Manhattan ������Ӌ�M�Еr����A�����@�N�C�Ϸ����� ASIC ��Ч���ܺõ�ԭ�����B�Ӿ�����ز��á��@��ζ���c�^��IJ��ֺͲ����OӋ���P���ӕr�c�C����������Ӌ�ĽY�����зdz��õ����P�ԡ�

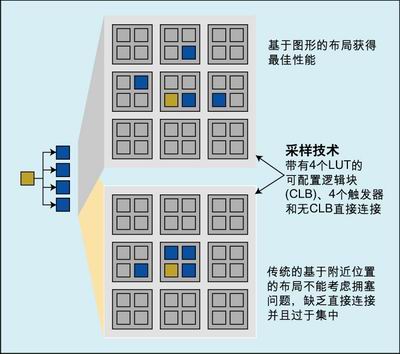

�� 2002 �굽 2003 �����g�_ʼ���ܶ�� EDA �������_ʼ���]���� ASIC �еõ��ľ����������R�ľC�ϼ��g���õ� FPGA �OӋ�У������������]���Mһ�����@�N˼·������ȥ���� Synplicity ��˾�µĻ��ڈD�εľC�Ϸ�����һ�����⣬�F�ڛ]�й��������ṩ���в������R�� RTL �C�Ϲ������� FPGA �OӋ�����}�ǣ��c ASIC �е��B�� �� ���� �� ��ͬ���ǣ� FPGA ���й̶��������A�ȴ_���IJ����YԴ�����������еIJ������O�ó�һ�� ( ijЩ�B�����ҿ죬ijЩ�L���죬ijЩ�̶�����ijЩ�L���� ) ��

���ڌ��H����r���ԣ����� ASIC �ľ����������R�ľC�Ͽ��Ը����γ��OӋ���Ѳ��ֆ�Ԫ�ĸ������M�в����͕r���Ӌ�������� FPGA ���f�����ɂ�߉���ܷ��������ą^(q��)��һ���܌��F����֮�g�Ŀ����B�ӡ� - ȡ�Q�ڿ��õIJ����YԴ�������B�ӵ�߉���ܲ���λ�ø��h���ܷ����ܫ@�ø��õIJ����͕r��Y�����M���@��һ�c�`���������@���Ǟ�ʲô�� ASIC �OӋ�еÁ��ľ����������R�ľC�ϼ��g���� FPGA �ܘ��r�����ܵõ��^�ѽY����ԭ��ͬ�ӣ�ʹ���@Щ���g���OӋ������Ҫ�����ĕr��ǰ�� ( �C�� ) �c��� ( �����c���� ) ����֮�g���OӋ���ͣ��ԫ@�����P�Ժ͕r���Ք���

�c FPGA �ܘ����P��һЩ����

��Ԕ����B���ڈD�ε������C�ϸ���֮ǰ�����˽��OӋ�΄յď��s�Ժ���Ҫ������ǰ��Մ���ģ� FPGA ���й̶����B���YԴ�������B���ѽ������ã������������е�·������һ�ӵ� ( �ж̵ġ��еȵĺ��L���B������ÿ���B�������ܾ��п졢�еȻ����������� ) ��

�D 2 �����^���y(t��ng)�ͻ��ڈD�εIJ���

ÿ��·�������ܾ��ж��� �� ���^�c ��( �������·�ij��ڵ� ) ���@��Ć��}�ǣ�����ܾ���һ����Ѹ�ٵ،�һ����̖��Դ�c���� ( ����·���^������ڵ� ) ���ٵ��f��һ��Ŀ�ĺ��� ( ����·���^����ڵ� ) �Ŀ���·����Ȼ��������҂���һ���Ȳ����^�c

���P��x:

- ...2011/12/09 12:16��ʹ�û���ģ�͵��OӋ�M��������C�ʹ_�J

- ...2010/10/20 15:46��ʹ�û���ģ�͵��OӋ�yԇ�����_�l(f��)�����O��

- ...2010/09/09 14:15��ʹ�û���PXI�ăx���������P���g�M����һ��������Ľ��ՙC�㷨ԭ���_�l(f��)

- ...���D��Ԕ����܇�x���屳���܇Ҏ(gu��)����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y(t��ng)

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�(�m(x��))

- ...���������ʽ�ضșz�y���y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y(t��ng)�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^(q��)�e

- ...�� ��о��(chu��ng)�����ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l(w��i)�{ɽ������(chu��ng)�¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B(t��i)朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ(gu��)����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�(chu��ng)������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I(y��)��(chu��ng)�°l(f��)չ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I(y��)�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I(y��)�l(f��)չ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä�(chu��ng)�£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İl(f��)չ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�l(f��)չ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l(f��)���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y(t��ng)���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y(t��ng)�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y(t��ng)�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y(t��ng)�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ��(ji��)�c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇