基于嵌入式DSP應用的低功耗優化策略

德州儀器公司 Scott Gary

無線系統及有線系統設計師均必須重視電源效率問題,盡管雙方的出發點不盡相同:對于移動設備而言,更長的電池使用壽命、更長的通話時間或更長的工作時間都是明顯的優勢,降低電源要求意味著使用體積更小的電池或選擇不同的電池技術,這在一定程度上也緩解了電池發熱問題;對于有線系統而言,設計師可通過減小電源體積、減少冷卻需求以及降低風扇噪聲來提高電池效率。人們很少會提到這樣一個事實:提高電源效率還可節省空間,而節省的空間可以用來增加能夠提高系統性能的組件,尤其是設計小組希望添加一個以上處理器時,這一點非常重要。

設計嵌入式DSP處理器或系統功耗要求嚴格的系統時,采用DSP專用技術、操作系統及其支持軟件可以降低功耗。超越傳統技術的DSP或雙處理器設計在節約能量方面表現出色。

功耗基礎知識

互補金屬氧化物半導體(CMOS)電路的總功耗是動態功耗與靜態功耗之和:

當門發生邏輯狀態轉換并產生內部結點充電所需的開關電流以及P通道及N通道同時暫態開啟引起直通電流時,就會出現動態功耗。通過以下公式可以估算其近似值:

其中,Cpd為動態電容,F為開關頻率,Vcc為電源電壓,而Nsw為轉換的比特數。另外,電壓(Vcc)決定著穩定工作狀態下的較大開關頻率(F)。上述關系中包含兩個重要概念:動態功耗與開關頻率呈線性關系,與電源電壓呈二次關系;較大安全開關頻率取決于電源電壓。為便于本文討論,將特定的頻率及電壓對稱為“設定點”。

很顯然,降低CPU時鐘速率將相應成比例地降低動態功耗,由于動態功耗與電源電壓成二次關系,在不影響系統性能的前提下,通過降低電壓就可能大大降低功耗。不過,對于特定任務集,降低CPU時鐘速率也會成比例地延長執行該任務集的時間,因此必須仔細分析應用以確保滿足其實時需求。

靜態功耗主要是由于晶體管漏電流造成的。一般說來,CMOS電路的靜態功耗很低,與其動態功耗相比可以忽略不計。嵌入式應用在不工作期間通常會“閑置”CPU時鐘以減少動態功耗,從而顯著降低總體功耗。而在未來的設計中必須特別關注靜態功耗問題,因為更高性能的新型晶體管的漏電流將顯著提高。

嵌入式系統常用技術

常用電源管理技術可以分為兩類:通過早期硬件設計決策時實現,或在系統運行時實現。設計早期的決策對滿足性能及功耗至關重要,下面列出了設計中需要考慮的十大要素,其中包括硬件選擇、設計策略及架構選擇。大多數要素都是嵌入式系統的基本要求,其他要素則需要單獨考慮。盡管下列決策是在設計早期制定的,但有些仍需在整個設計周期中進行再驗證。如下所列:

- 選擇低功耗組件;

- 分割電壓與時鐘域;

- 支持電壓及頻率調節功能;

- 啟用保持電壓門控功能;

- 通過軟件利用中斷減少輪詢;

- 采用分級存儲器模型;

- 降低輸出負載;

- 系統啟動時關閉非關鍵資源供電;

- 盡量減少活動PLL數量;

- 使用時鐘分頻器快速變換頻率。

確定系統架構以后,設計團隊需要將注意力轉向系統運行時環境。以下列出的14項,在設計過程中要始終關注其中大部分內容:

- 不需要時則關閉門控時鐘;

- 引導過程中主動關閉不必要的功耗;

- 僅在需要時用向子系統供電;

- 激活外設低功耗模式;

- 充分利用外設活動狀態檢測器;

- 使用自動刷新模式;

- 對應用進行基準測試來確定必需的較小頻率及電壓;

- 根據總體活動情況調整CPU頻率及電壓;

- 動態調節CPU頻率及電壓以匹配預計的工作負載;

- 優化代碼的執行速度;

- 使用低功耗代碼序列及數據模式;

- 使用代碼覆蓋技術減少對高速內存的需求;

- 更換電源時進入簡化功能模式;

- 平衡精確度與功耗的關系。

有經驗的設計團隊必須至少在概念上熟悉上述嵌入式系統應用設計要點(其中部分與DSP電路有關)。任何降低功耗的設計都有可能對性能產生負面影響或導致系統不穩定。

DSP RTOS如何滿足低功耗設計要求

一部分較重要的并得到普遍認可的技術方法可以融合到RTOS中,相關的技術包括:閑置、關閉活動電源、器件驅動程序通知、內存管理、電壓/頻率調節。然而,由于設計目標不盡相同,將這些技術構建到RTOS中并不容易。設計師需要在這些方法中做出選擇,設計的關鍵目標就是高效性、靈活性以及與操作系統本身的松散關系。

TI的DSP/BIOS操作系統的電源管理器(PWRM)非常適于用作現有RTOS的電源管理模塊。盡管以下描述的設計實現是針對DSP/BIOS,但其概念可很容易地運用到其他操作系統,甚至用于無操作系統的應用環境。

電源管理器的要求

電源管理器設計的關鍵要求如下:

- 管理決策必須由應用觸發,而不是操作系統觸發;

- 電源管理活動應當針對大部分應用代碼透明;

- 電源管理器必須支持電壓與頻率(V/F)調節,并充分利用芯片的空閑與睡眠模式;

- 電源管理器必須在應用代碼、驅動程序以及操作系統本身范圍內協調電源事件處理,并在發生特定事件時向客戶端發出通知;

- 電源管理特性必須在任何線程環境中可用,并且還必須對特定客戶端的多個實例可用(如一個器件驅動程序的多個實例);

- 在向客戶端發出電源事件通知時,電源管理器必須支持事件處理的延遲完成,并在等待延遲客戶端的完成信號的同時通知其他客戶端;

- 對具有不同功能的不同平臺,電源管理器必須是可擴展的和可移植的。

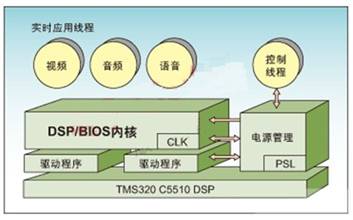

為滿足上述的關鍵要求,可將電源管理器作為DSP/BIOS的附屬模塊添加,如圖1所示。電源管理器位于內核之外,它不是系統中的一項任務,而是一組可在應用控制線程以及器件驅動程序環境中執行的API。

圖1. 電源管理器分區

這意味著無需修改內核,但在CPU時鐘與操作系統定時器時鐘相結合的平臺上,DSP/BIOS時鐘模塊(CLK)需要補充例程(routine),這對頻率縮放非常重要,因為這些例程能夠使OS時鐘適應PWRM的客戶端。

電源管理器通過寫入并讀取時鐘空閑配置寄存器,并通過控制CPU時鐘速率及穩壓電路的特定平臺功率擴展庫(PSL),直接與DSP硬件相連接。PSL將電源管理器及應用的其他部分與頻率和電壓控制硬件的低層實現細節相隔離。

電源管理器擁有若干個與應用相關的任務。由設計工程師對其進行靜態配置,并在運行時進行動態調用:

- 空閑時鐘域—電源管理器提供的接口可使特定時鐘域處于空閑狀態,從而降低功耗。此外,它還可以在OS空閑循環的適當點提供能自動使DSP CPU和高速緩存處于空閑狀態的機制。

- 降低引導時間的功耗—電源管理器包含一個鉤子機制(hook mechanism),這使開發人員能夠設定省函數,以便在引導時間實現自動調用。

- 電壓及頻率(V/F)調節—電源管理器提供的接口可使應用程序動態更改DSP內核的工作電壓及頻率。因此,應用程序可利用該特性根據相關的處理要求相應調整功耗。電源管理器API可設定應用中的電壓是否應隨同頻率進行調節,以及在降壓轉換過程中是否可繼續執行任務,轉換時延由負載而定,有可能會較長;如果處理器在降壓轉換期間工作正常,則允許繼續執行應用;此外,電源管理器還包含用于查詢V/F設定點屬性及時延的API。

- 睡眠模式—電源管理器包含的配置及運行時接口使開發人員可產生自定義睡眠模式,以便在非工作狀態期間節省電能。

- 電源事件的注冊及通知—為了調整整個應用中的V/F調節比例、睡眠模式以及其他事件,電源管理擁有一套記錄及通知機制,以使諸如應用代碼、外設驅動程序、打包的內容以及OS時鐘模塊能針對會影響到他們的特定事件進行記錄,以便通知。這些電源事件如“即將更改 V/F 設定點”、“完成更改V/F 設定點”、“進入睡眠模式”、“從睡眠模式中喚醒”以及出現“電源故障”等。通知進程(notification process)是電源管理器的重要特性。當無需通知時可使用“未登記”功能。

策略實施

上面已經建立了提高電源效率的基礎,下一步工作就應該確定開發高效率應用的策略,并充分利用OS中的部分方法及支持。

所建議的策略包括以下11個步驟。該策略具有可重復性:當無法滿足電源管理目標,或者需要采用額外的運行時方法才能滿足應用的電源預算時,就可重復這些步驟。

- 從較初就考慮到電源效率;

- 選擇低功耗組件;

- 對電源進行建模和估測,并進行相應的硬件測試;

- 針對電源管理和測量設計具備鉤子機制的硬件;

- 構建可大幅提高工作效率的軟件;

- 啟用簡單的電源管理開/關機切換;

- 在無電源管理的情況下也可先進入工作;

- 重復開啟“開機”特性,并測量功耗開銷(payoff);

- 開啟代碼生成優化功能、重置代碼及數據,并調整“熱點”監測;

- 進行校準,以實現頻率及電壓的較低;

- 激活并應用所有的電源管理特性。

選用現成的DSP*估板5509A EVM PLUS板作為測試平臺,該*估板不僅支持V/F調節,還包含針對DSP內核與總體系統電源測量的鉤子機制。

需要注意的是,EVM作為易于使用的*估平臺,并未在出廠時提供較佳功耗配置。另外,在*估效果時應謹記由于其易于配置,所以EVM上測量的總體系統電源數量就應多于通常情況下部署的平臺。EVM還能以DSP內核級與系統級兩種方法測量各種技術的有效性。

相關閱讀:

- ...2015/01/21 17:14·基于嵌入積分滑模策略的船舶運動控制

- ...2010/06/11 15:15·一種基于嵌入式系統和Internet的FPGA動態配置方案

- ...2009/09/28 11:34·基于嵌入式處理器軟核Nios II的IP復用技術及應用

- ...2009/09/27 16:30·基于嵌入式系統的虛擬儀器設計

- ...2009/09/27 15:49·基于嵌入式系統的機械車載監控終端研究

- ...· Efinix® 全力驅動AI邊緣計算,成功推出Trion™ T20 FPGA樣品, 同時將產品擴展到二十萬邏輯單元的T200 FPGA

- ...· 英飛凌亮相進博會,引領智慧新生活

- ...· 三電產品開發及測試研討會北汽新能源專場成功舉行

- ...· Manz亞智科技跨入半導體領域 為面板級扇出型封裝提供化學濕制程、涂布及激光應用等生產設備解決方案

- ...· 中電瑞華BITRODE動力電池測試系統順利交付北汽新能源

- ...· 中電瑞華FTF系列電池測試系統中標北京新能源汽車股份有限公司

- ...· 中電瑞華大功率高壓能源反饋式負載系統成功交付中電熊貓

- ...· 中電瑞華國際在電動汽車及關鍵部件測評研討會上演繹先進測評技術